# **ISim Timing Diagrams**

By:

Sebastian Hoyos

# Quick VHDL

- Entity: Describes the interface

- Architecture: Actual implementation

### **AND Gate**

```

-- (this is a VHDL comment)

-- import std_logic from the IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- this is the entity

entity ANDGATE is

port (

IN1 : in std_logic;

IN2 : in std_logic;

OUT1: out std_logic);

end ANDGATE;

architecture RTL of ANDGATE is

begin

OUT1 <= IN1 and IN2;

end RTL;

```

# ISim Project File Syntax

- verilog|vhdl <library\_name> {<file\_name>.v|.vhd}

- *verilog | vhdl* indicates that the source is a Verilog or VHDL file. Include either verilog or vhdl.

- library\_name> indicates the library that a particular source on the given line should be compiled. "work" is the library.

- <file\_name> is the source file or files associated with the library.

```

File Edit Format View Help

vhdl work "..\sources\drp_stmach.vhd"

vhdl work "..\sources\drp_demo.vhd"

vhdl work "..\sources\drp_demo_tb.vhd"

vhdl work "..\sources\drp_dcm.vhd"

vhdl work "..\sources\drp_dcm.vhd"

vhdl drp_tb_lib "..\sources\drp_tb_pkg.vhd"

```

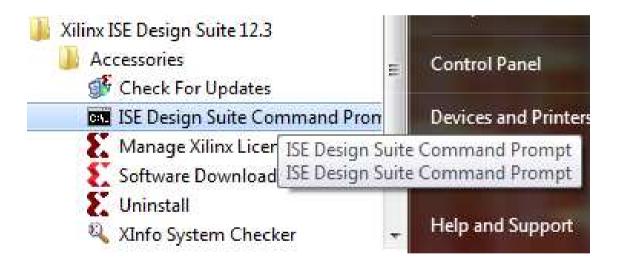

# Building the Simulation .exe

Open Command Prompt

# Building the Simulation .exe

• The following is opened:

```

ISE Design Suite Command Prompt

C:\Xilinx\12.3\ISE_DS>

```

# Building the Simulation .exe

Without any parameters:

```

ISE Design Suite Command Prompt

C:\Xilinx\12.3\ISE_DS>fuse

Running: C:\Xilinx\12.3\ISE_D$\ISE\bin\nt64\unwrapped\fuse.exe

ISim M.70d (signature 0x16fbe694)

Number of CPUs detected in this system: 2

Turning on mult-threading, number of parallel sub-compilation jobs: 4

ERROR:Šimulator:747 - No design top(s) specified

ISim M.70d (signature 0x16fbe694)

Usage: C:\Xilinx\12.3\ISE_DS\ISE\bin\nt64\unwrapped\fuse.exe [options] [libname.

lunitname...

(Switches with double dash '--' can also be used with a single dash '-')

ISim fuse options:

Read additional options from the specified

-f [ --file ] arg

-h [ --help ]

Print this help message

--version

Print the compiler version

Display messages according to specified st

--intstyle arg

yle: ise!xflow|silent|default (Default: de

fault)

Specify Xilinx ISE file

--ise arg

--incremental

Compile files only if they have changed si

nce the last compile

--initfile arg

Use user defined simulator init file to ad

d to or override the settings provided by

the default xilinxsim.ini file

```

## Fuse.exe Syntax

- fuse –incremental –prj <project file> -o

<simulation executable> library.top\_unit>

- -incremental: requests fuse to compile only the files that have changed since the last compile

- -prj: specifies an ISim project file to use for input

- -o: specifies the name of the simulation executable output file

C:\Xilinx\12.3\ISE\_DS>fuse.exe -incremental -prj simulate\_isim.prj -o simulate\_i sim.exe work.drp\_demo\_tb

## Running the Sim .exe

- Executable is created by fuse.exe

- This .exe calls the Simulator

- Double click does nothing, needs parameters

- We got to invoke the GUI mode

# Simulation .exe Syntax

- Simulation\_executable –gui -wdb

<waveform\_database\_file>

- -gui: launches ISim in GUI mode.

- -wdb: specifies the file name of the simulation database output file.

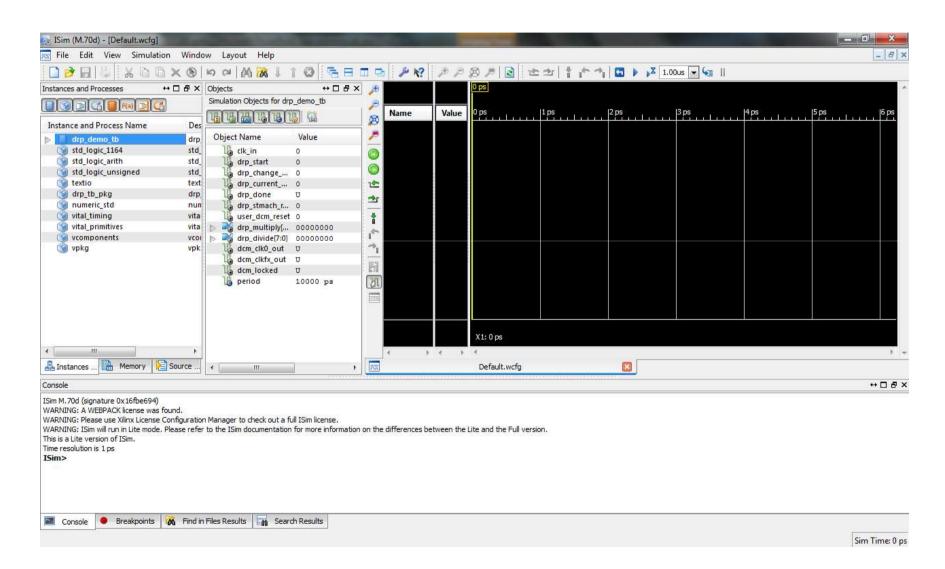

### Isim GUI

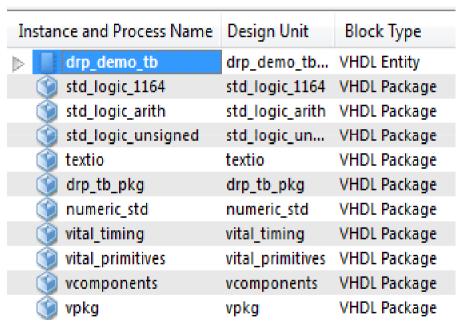

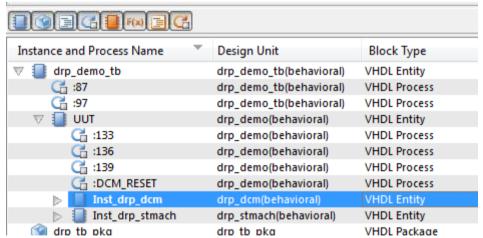

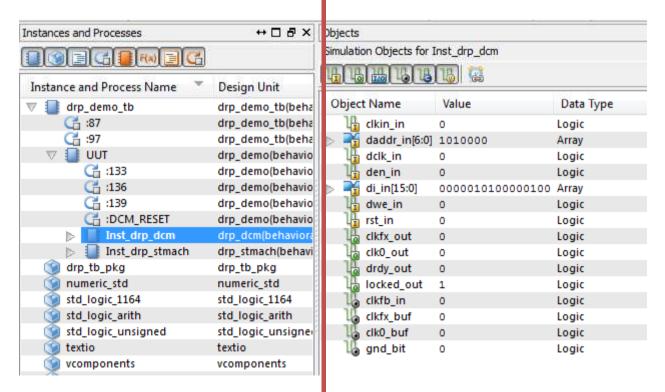

### Instances and Processes

- Displays the block (instance and process) hierarchy associated with the wave configuration open in the Wave window.

- Instantiated and elaborated entities/modules are displayed in a tree structure, with entity components being ports, signals and other entities/modules.

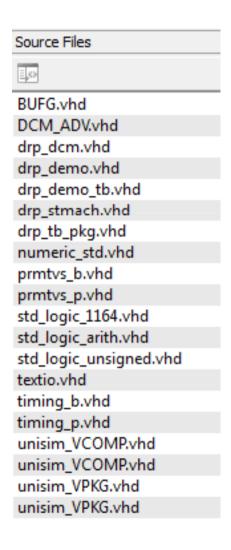

### Source Files Panel

- Displays the list of all the files associated with the design.

- The list of files is provided by the **fuse** command during design parsing and elaboration.

- The HDL source files are available for quick access to the read-only source code.

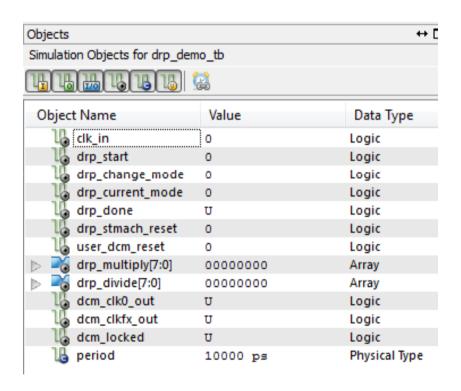

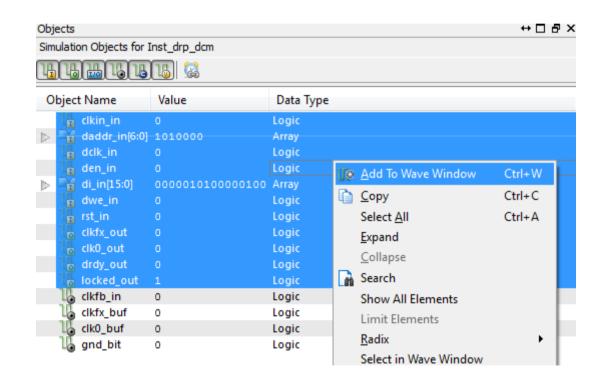

# **Objects Panel**

- Displays all ports and signals associated with the selected instances and processes in the Instances and Processes panel.

- Object Name Displays the name of the signal, accompanied by the symbol which represents the type of object it is.

- Value The value of the signals at the current simulation time or at the main cursor, as determined by the Sync Time toolbar button.

- Data Type Displays the data type of the corresponding simulation object, logic or an array.

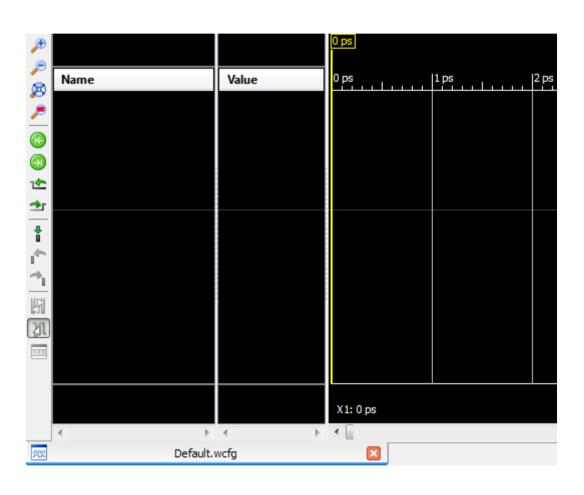

### **Wave Window**

- Displays signals, buses, their properties and any other wave objects.

- The wave configuration is used to drive the simulation

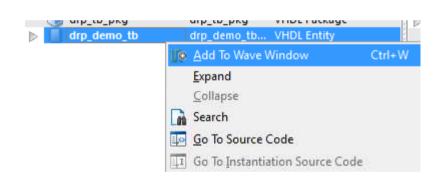

# Configuring the Wave Window

- Select the VHDL Entity and right click on it. The entity is the one with the ports, buses and signals.

- Choose "Add to Wave Window"

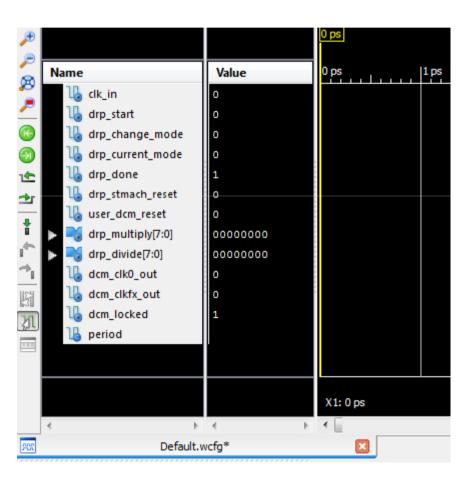

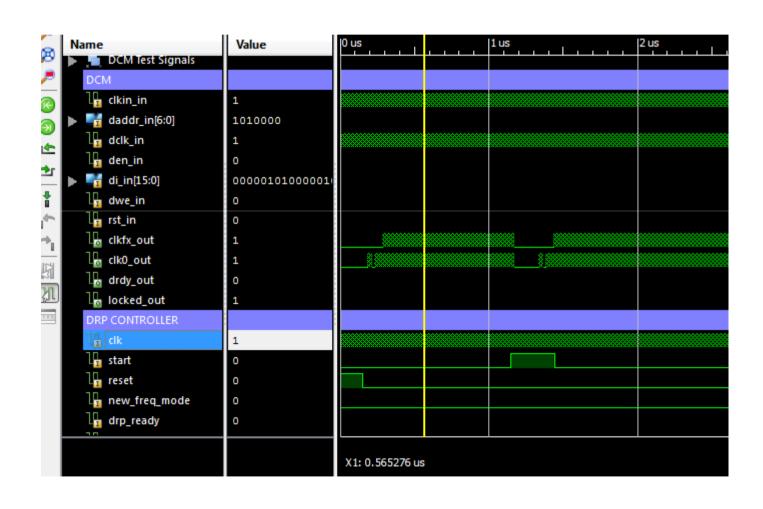

# Wave Window with Signals

- Signals, ports and buses added.

- The values are the one listed in the Objects

Panel

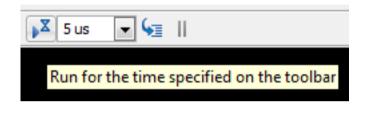

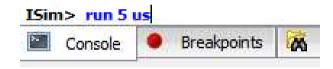

## Running the Wave Sim for a Specified Time

- Type 5 us in the Simulation Time field and press Enter or click the "Run For" button

- Type run 5 us in the Console prompt

- If Simulation doesn't start, press the "Restart" option

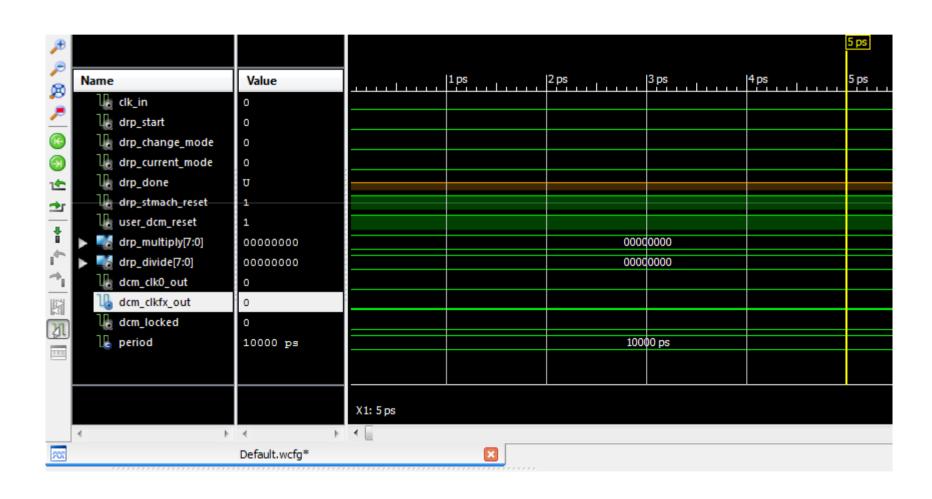

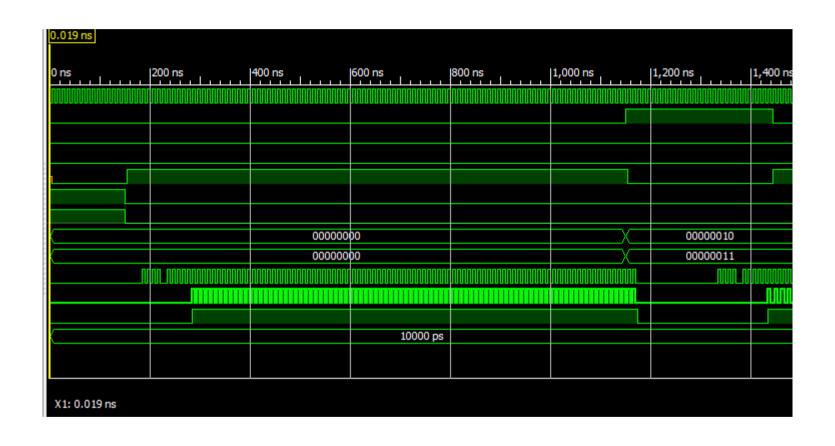

### Wave Sim Results

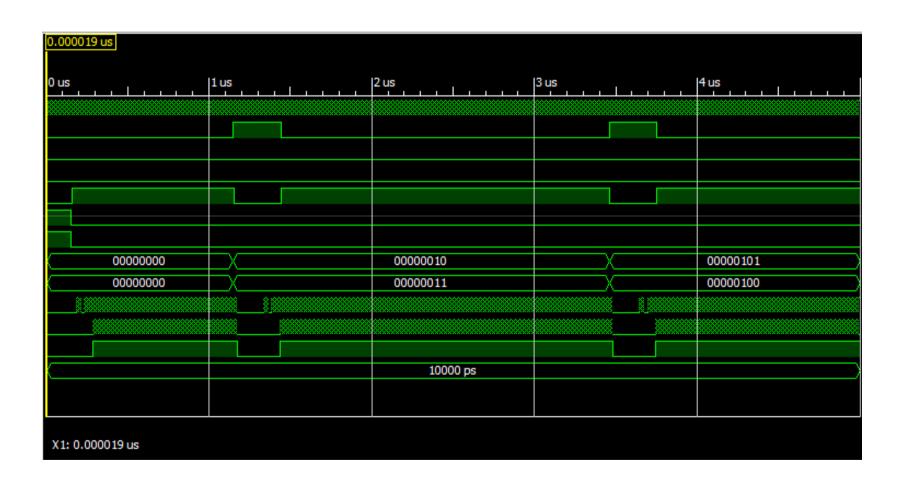

### **Zoomed Out Wave Sim Results**

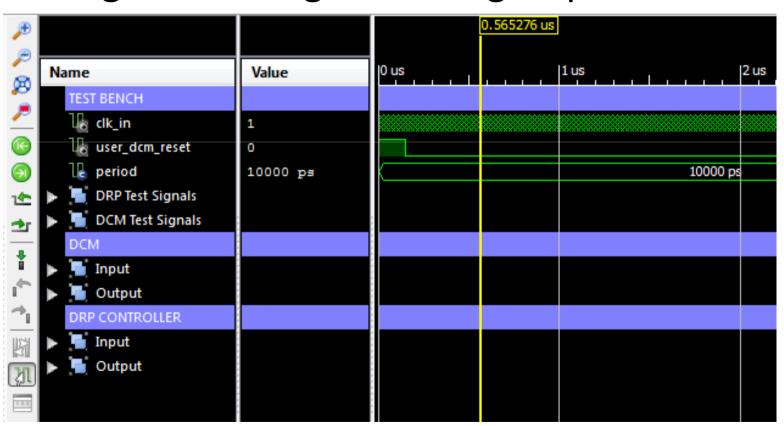

## **Full Simulation**

# Now... lets make it pretty (unlike this PowerPoint)

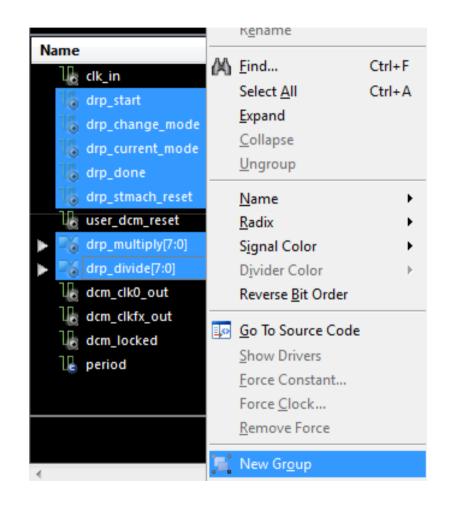

### Groups

- Hold Ctrl and select the signals in the wave window

- Right click on any of them

- Select "New Group" in the menu

- Name the group

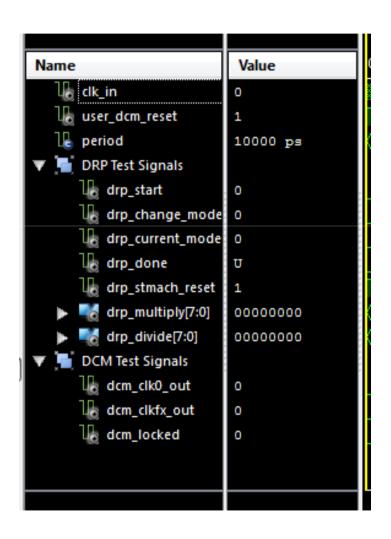

### Groups

- End Result ->

- You have to expand the group to see the signals

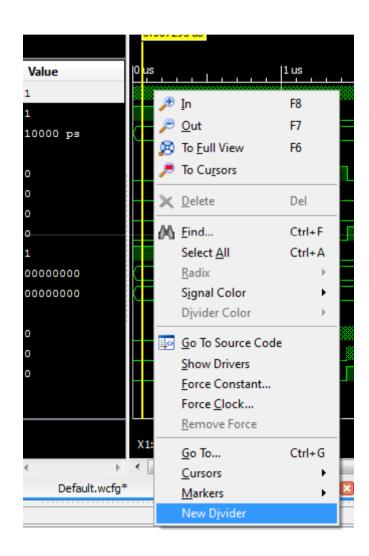

### **Dividers**

- Right Click on any part of the Wave Window

- Select New Divider

- Name it

- Move it to where you want it to be

- Rename them by double clicking on them or using F2

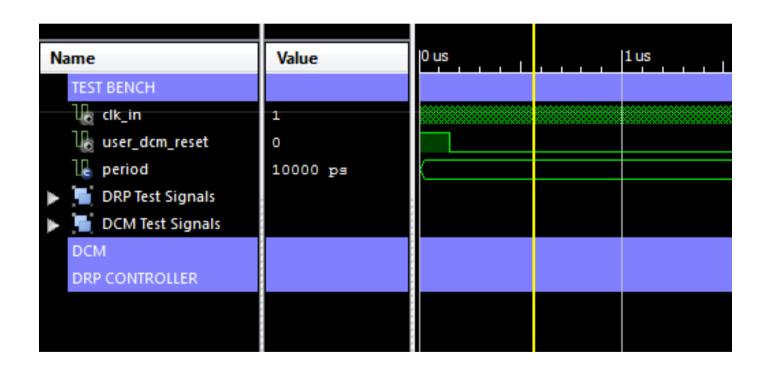

## **Dividers**

• End Result:

# Adding Signals from Sub-Modules

- Allows you to study the interaction between the sub-modules and the test bench test signals

- This interacts with an entity that is in a deeper level

Expand the test bench entity until you see the instanced entities

# Objects from the instanced entity

You'll get the following instances:

You'll get the following signals:

# Adding the Signals

- Select the signals

- Right Click

- Add to Wave Window

# Added the Signals

# Organized by Groups

The signals are organized in groups

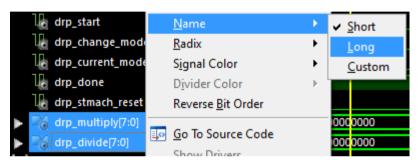

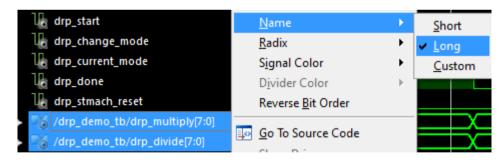

# Naming the Signals

• Name:

Select Long

Use Custom for setting a desired name

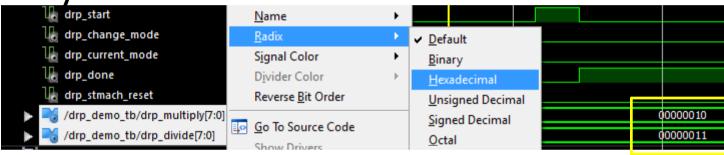

### Radix

• Binary:

• Select Hexadecimal:

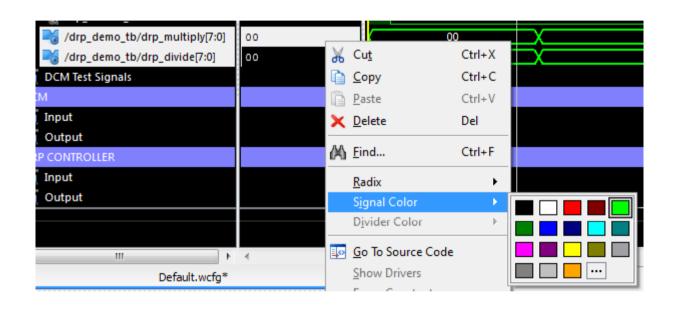

# Crayola Effect

Changing the Color:

| \[     \big  \left\] /drp_demo_tb/drp_multiply[7:0] |    | 00 |  | 02 |

|-----------------------------------------------------|----|----|--|----|

| /drp_demo_tb/drp_divide[7:0]                        | 00 | 00 |  | 03 |

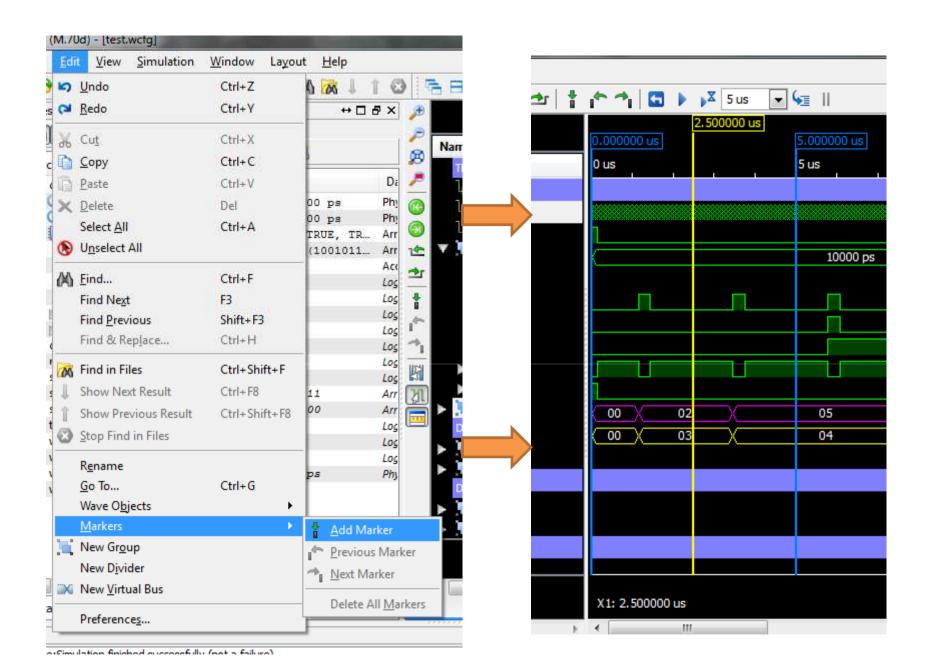

### Markers

- Useful to identify times in the diagram

- Most used to determine when a test starts

- The tests are defined in the test bench file

- Measuring time between 2 endpoints

- Useful for calculating the frequency of a signal

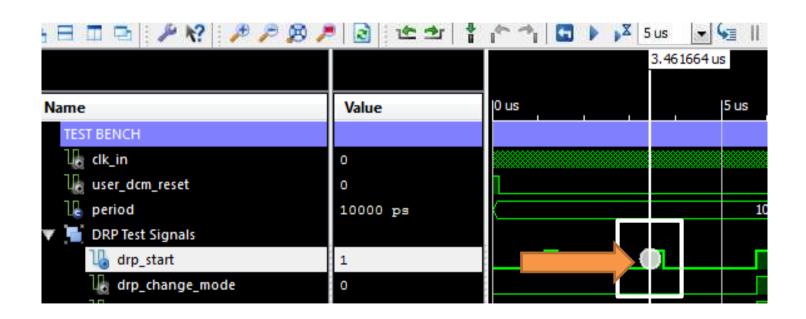

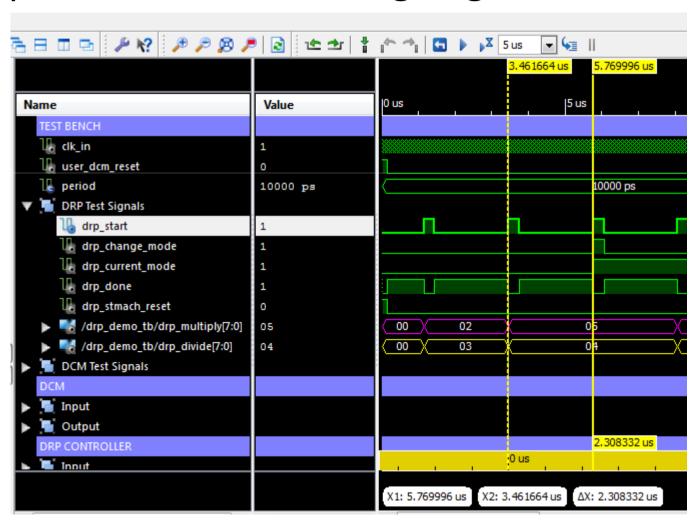

• 1st: Click on the Snap to Transition toggle button

Drag the cursor over a signal until it snaps on a rising edge

Repeat for a second rising edge

• The time difference is

$$\Delta X = 2.308332 \,\mu s$$

$$f = \frac{1}{\Delta X} = 433.213 \ KHz$$