# VHDL: A "Crash" Course

### Dr. Manuel Jiménez

With contributions by: Irvin Ortiz Flores

Electrical and Computer Engineering Department University of Puerto Rico - Mayaguez

### Outline

- Background

- Program Structure

- Types, Signals and Variables

- Description Styles

- Combinational Logic Design

- Finite State Machines

- Testbenches

### What is VHDL?

- VHDL: VHSIC Hardware Description Language – VHSIC= Very High Speed Integrated Circuit

- VHDL was created for modeling digital systems

Language subset used in HW synthesis

- Hierarchical system modeling

- Top-down and bottom-up design methodologies

### **VHDL Retrospective**

- VHDL is an IEEE and ANSI standard for describing digital systems

- Created in 1981 for the DoD VHSIC program

- First version developed by IBM, TI, and Intermetric

- First release in 1985

- Standardized in 1987 and revised several times thereafter

- Standard 1076, 1076.1 (VHDL-AMS), 1076.2, 1076.3

- Standard 1164, VHDL-2006

- Inherits many characteristics of ADA: Strong typed

## **VHDL Uses**

- Modeling of Digital Systems

Looks a High-level Language

- Synthesis of Digital Systems

- Language Subset

- Synthesis Targets

- FPGAs & FPLDs

- ASICs

- Custom ICs

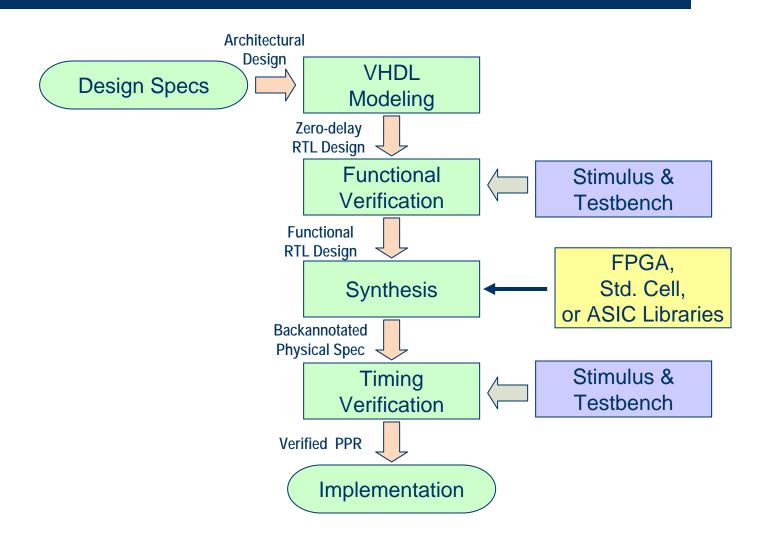

### **VHDL-based Design Flow**

### **Common VHDL Data Types**

- Integer: Predefined in the range -(2<sup>31</sup>) through +(2<sup>31</sup>-1). Subtypes can be declared

- Boolean: False, True

- <u>Bit, std\_logic</u>: A single bit

- <u>Bit\_vector, std\_logic\_vector</u>: Multiple bits

Range needs to be specified

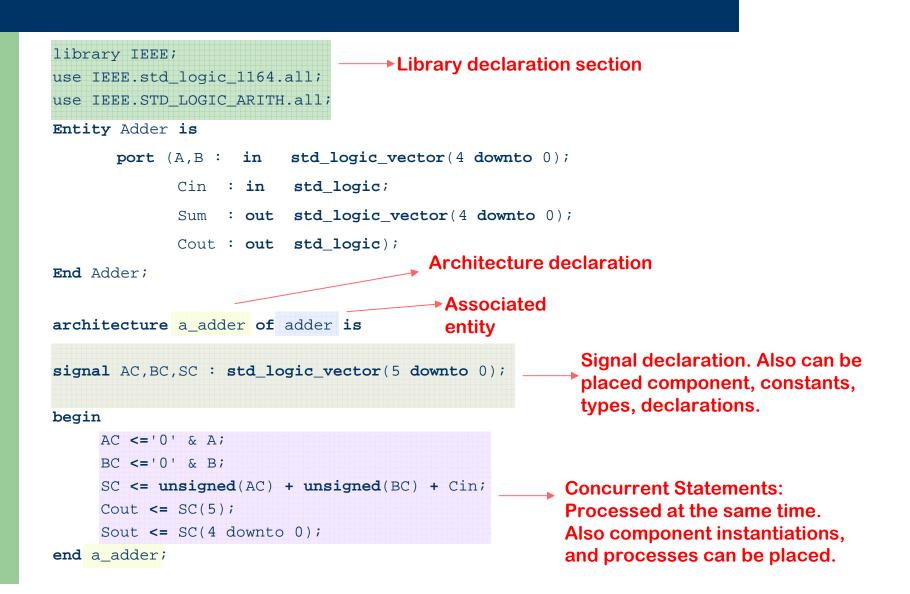

### **Basic VHDL Program Structure**

library IEEE; Library use IEEE.std logic 1164.all; **Inclusion** use IEEE.STD\_LOGIC\_ARITH.all; Entity Adder is port (A,B : in std logic vector(4 downto 0); Entity Cin : in std logic; **Declaration** Sum : out std logic vector(4 downto 0); Cout : out std logic); End Adder; architecture a adder of adder is signal AC, BC, SC : std\_logic\_vector(5 downto 0); begin AC <= '0' & A; Architecture BC <= '0' & B; **Declaration** SC <= unsigned(AC) + unsigned(BC) + Cin;</pre> Cout  $\leq SC(5);$ Sout  $\leq SC(4 \text{ downto } 0);$ end a adder;

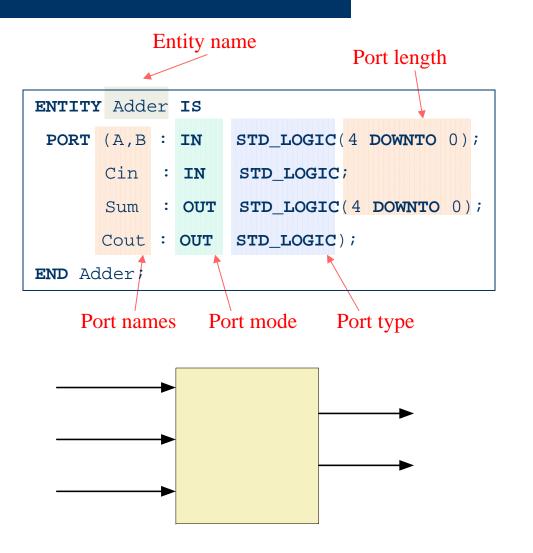

### **Entity Declaration**

- Specifies interface

- States port's name, mode, & type

- Mode can be IN, OUT, or INOUT

- Port type can be from a single bit to a bit vector

### **Architecture Declaration**

- Describes the internal operation of an entity

- Several architectures can be associated to one entity

- States which components, signals, variables, and constants will be used

### An Architecture Example

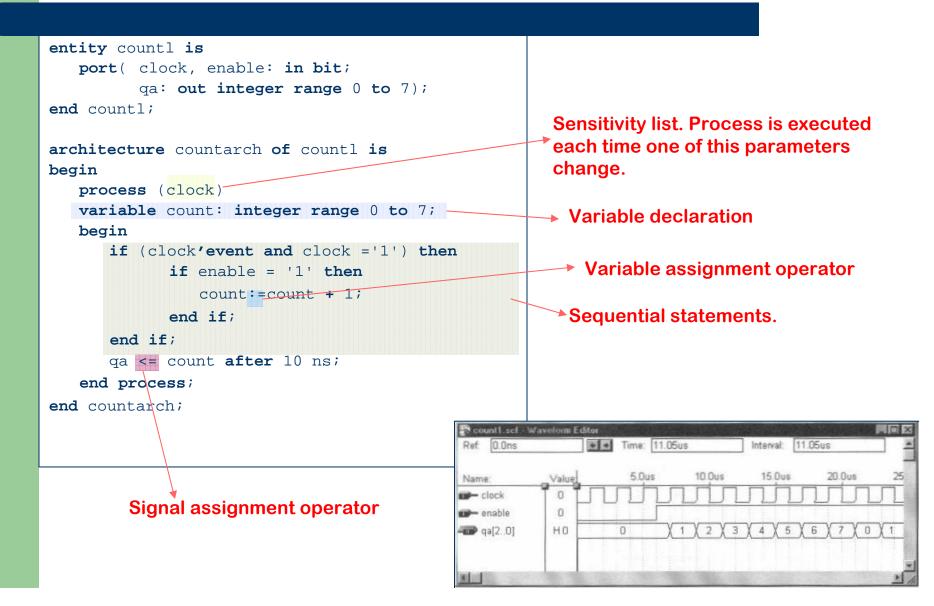

### Signals Vs Variables (1/2)

#### Signals

- Can exist anywhere, like wires

- Connect components or carry information between processes

- When inside a process, its value is updated when the process suspends

- Signal assignment operator: <=</li>

- Variables

- Can only exist inside a process

- Behave like local HLL variables holding temporary values

- Values updated right after assignment.

Sequence matters

- Variable assignment operator: :=

### **Concurrent Vs. Sequential Code**

- Concurrent Statements

- Occur typically outside a process

- Take place concurrently, i.e. with simulation clock stopped

- Uses of SIGNALS and processes

- Sequential Statements

- Occur only inside a process

- Are executed sequentially, i.e. one after another

- Uses VARIABLES and functions

## Signals Vs Variables (2/2)

#### Signals

- Initial values: A=5, B=15, X=10

- Final values: A=10, B=5

```

Sigproc: process(A,X)

Begin

```

```

A <= X;

```

B <= A;

End process Sigproc;

#### Variables

- Initial values: A=5, B= 15, X=10

- Final values: A=10, B=10

Sigproc: process(X)

Variable A,B : integer;

Begin

A := X;

B := A;

End process Sigproc;

### **Three-Bit Binary Counter**

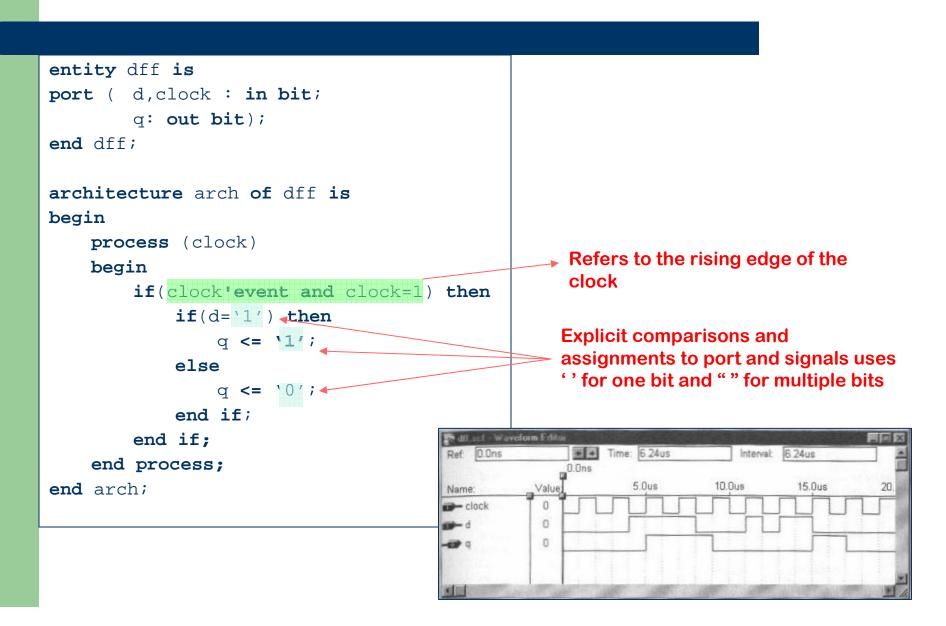

## A "D" Flip-Flop

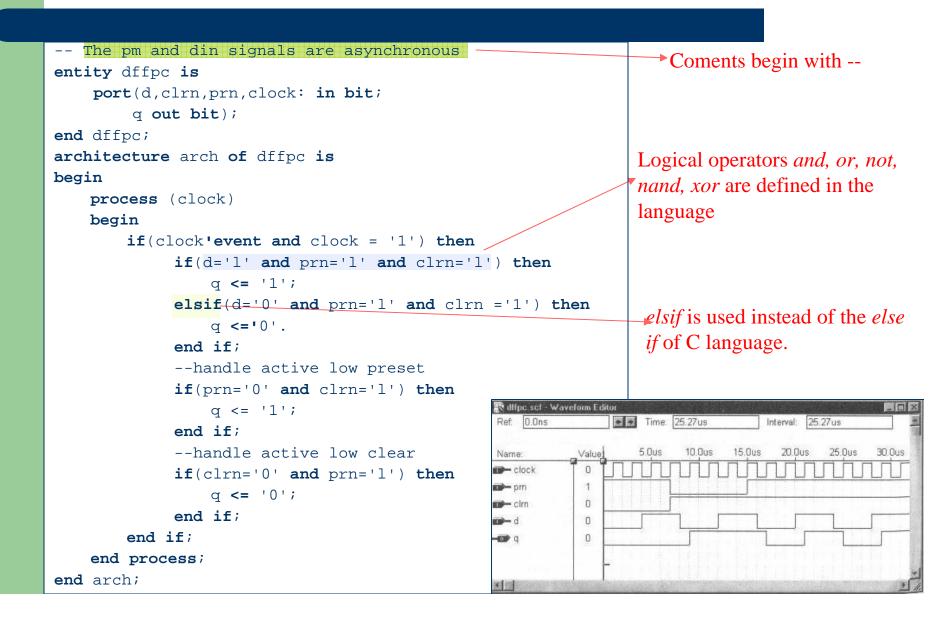

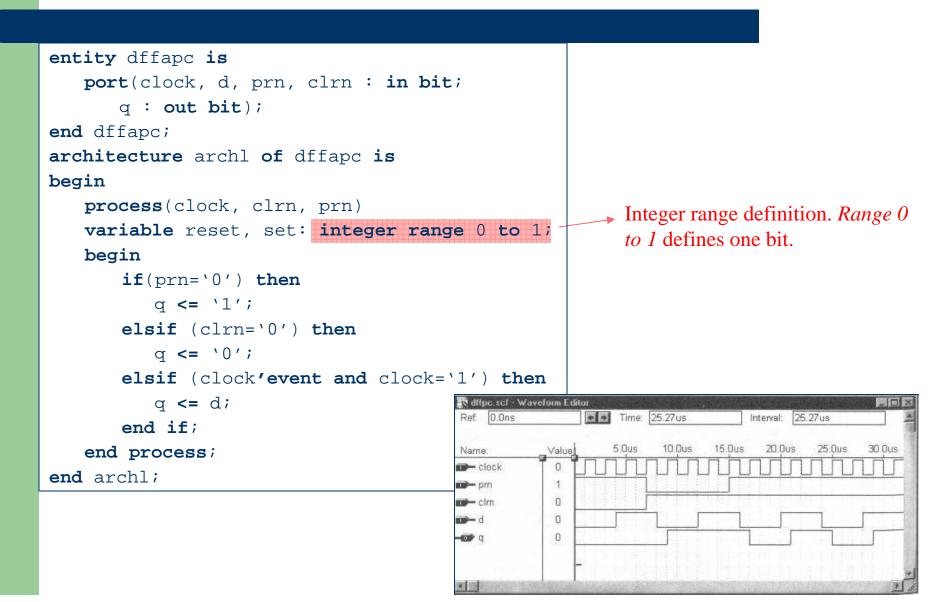

### D-type flip-flop with active low preset and clear inputs

### D Flip-Flop with Asynchronous Preset and Clear

### **Full Adder**

```

library ieee;

use ieee.std_logic 1164.all;

entity fulladd is

port( al,a2,cin: in std_logic;

sum,cout: out std_logic);

end fulladd;

architecture fulladd of fulladd is

begin

process(al,a2,cin)

begin

sum <= cm xor al xor a2;

cout <= (al and a2) or (cin and (al xor a2));

end process;

end fulladd;

```

| 😵 fulladd.set - | Wavetorm Edito |             | Statistical Statistics |                |       |

|-----------------|----------------|-------------|------------------------|----------------|-------|

| Ref: 0.0ns      |                | Tims: 784.0 | ns                     | Interval: 784. | Ons   |

| Name:           | Value          | 400.0ns     | 800.0ns                | 1,2us          | 1.6us |

| 🗊 — cin         | 0              |             |                        |                |       |

| <b>ii)-</b> a2  | 0              |             |                        |                |       |

| 🕬 a1            | 0              |             |                        |                |       |

| -🐼 sum          | 0              |             |                        |                |       |

| - cout          | 0              |             |                        |                |       |

|                 |                |             |                        |                |       |

| <u>.</u>        | Provide State  |             |                        |                | Þ     |

### **Four Bit Adder**

```

--A VHDL 4 bit adder

entity fourbadd is

port ( cin: in integer range 0 to 1;

addend1:in integer range 0 to 15;

addend2:in integer range 0 to 15;

sum: out integer range 0 to 31);

end fourbadd;

architecture a4bitadd of fourbadd is

begin

sum <= addend1 + addend2 + cin;

end a4bitadd;</pre>

```

Integer type allows addition, subtraction and multiplication. Need the following statement at the library declaration section:

```

use IEEE.STD_LOGIC_ARITH.all

```

| Ref: 0.0ns |        | * +    | Time: 255.0ns |                                     | Int       | Interval: 255.0ns |       |         |         |      |

|------------|--------|--------|---------------|-------------------------------------|-----------|-------------------|-------|---------|---------|------|

| Name:      | Value: | 200    | .Ons 400      | ),Ons 600                           | ),Ons 800 | l.Ons             | 1.Qus | 1.2us   | 1.4us   | 1.6u |

| 产 cin      | 0      | T      |               | 1                                   |           | 1                 |       |         |         |      |

| 🗭 addend1  | но     | 0 (1)  | (2)(3)        | $\left( 4 \right) \left( 5 \right)$ | X 6 X 7   | (8)               | A) (A | (в(с)   | (D)(E   | (F)  |

| 🗩 addend2  | H2     | 2)(3)  | (4)(5)        | 6 7                                 | <u> </u>  | AXE               | s)(c  | (D(E)   | (F)(0   |      |

| sum        | H 02   | 02 104 | ¥07 Y09       | NOA YOU                             | OF V11    | ¥12Y              | 14 11 | 7 19 1A | Vic Voi | 11   |

### **VHDL Description Styles**

- <u>Dataflow</u>: Uses concurrent signal assignments

- <u>Behavioral</u>: Relies on process to implement sequential statements

- <u>Structural</u>: Describes the interconnections among components of a system. Requires hierarchical constructs.

- Mixed Method: Combines the three styles.

#### **D** Flip-Flop Dataflow

```

--D flip-flop dataflow

--Includes preset and clear

entity dff_flow is

port (d, prn, clrn: in bit;

q,qbar: out bit);

end dff_flow;

```

```

architecture archl of dff_flow is

begin

```

```

q <= not prn or (clrn and d);</pre>

```

```

qbar <= prn and (not clrn or not d);</pre>

```

end arch1;

| Ref. 0.0ns |         | Ons Time: 10 | Time: 108.0ns |       | 108.0ns |

|------------|---------|--------------|---------------|-------|---------|

| Name: ,    | _Value: | 50.0ns       | 100.0ns       | 150.0 | ns 2    |

| 产 cim      |         |              |               |       |         |

| 产 prn      | 0       | Π            |               | 1111  | 1111    |

|            |         |              |               | 1     |         |

| 🗲 d        | 0       |              |               |       | 1 1 1   |

| ∎—d<br>@Pq | 1       |              |               |       |         |

### **Behavioral D Flip-Flop**

```

--Active low preset and clear inputs

entity dffpc2 is

port(d,clock,clrn,prn:in bit;

q,qbar:out bit;

end dffpc2;

architecture arch of dffpc2 is

begin

process(clock,clrn,prn)

```

```

begin

if(clock'event and clock = `1')

then

q <= not prn or (clrn and d);</pre>

```

| Ref: 370 | .Ons   | * * | Time: 0.2ns | Interval: | -369.8ns |

|----------|--------|-----|-------------|-----------|----------|

| Name:    | Value: | L   | 100.0ns     | 200.0ns   | 300.0ns  |

| 🕞 clock  | 1      | ไกม | www         | UUUU      | UUU      |

| u cirn   | 1      |     |             |           |          |

| 🗩 pm     | 1      |     |             |           |          |

| d 🖌      | 0      |     |             |           |          |

| - 🔊 q    | 1      |     |             |           |          |

| - qbar   | 0      |     | 1           | TH.       |          |

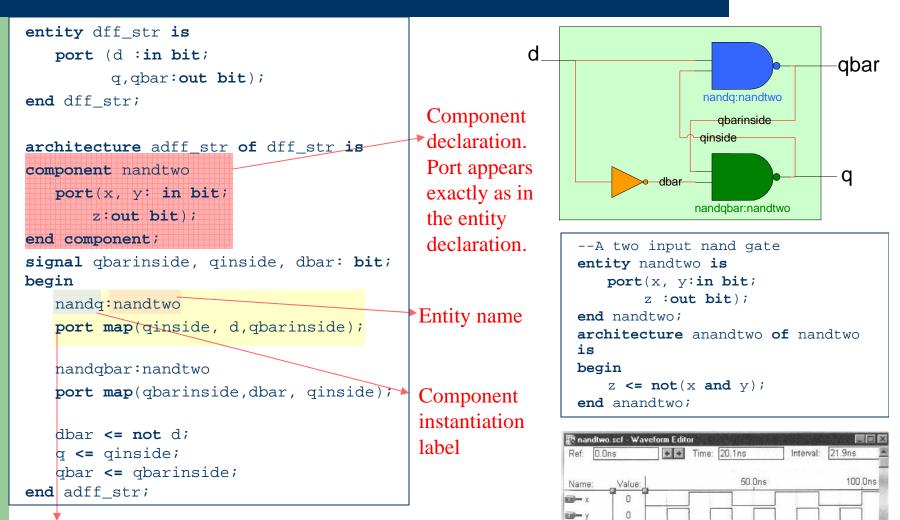

### **D** Flip-Flop Structural

2 🐨

4

1

Component instantiation. Connections are made by correspondence

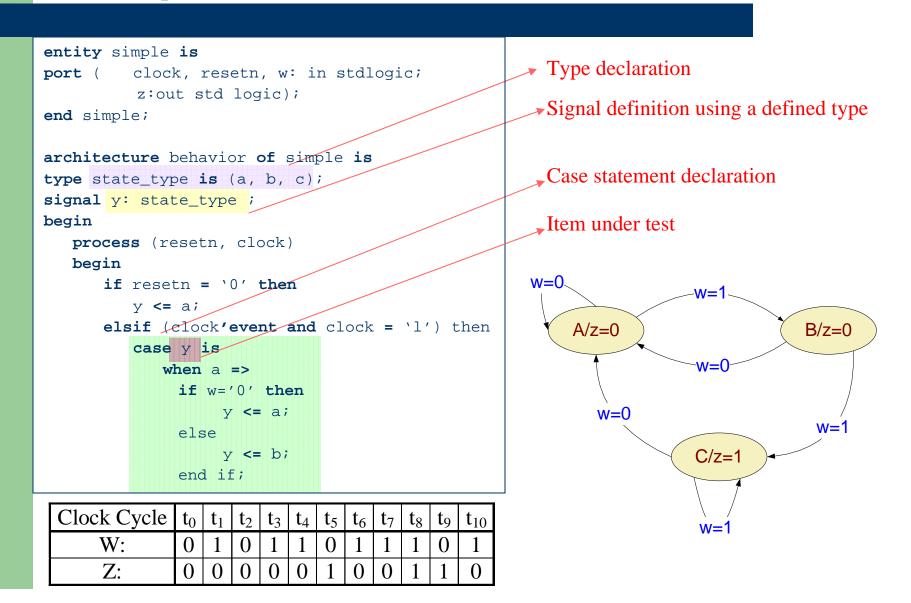

#### **A Sequence Detector**

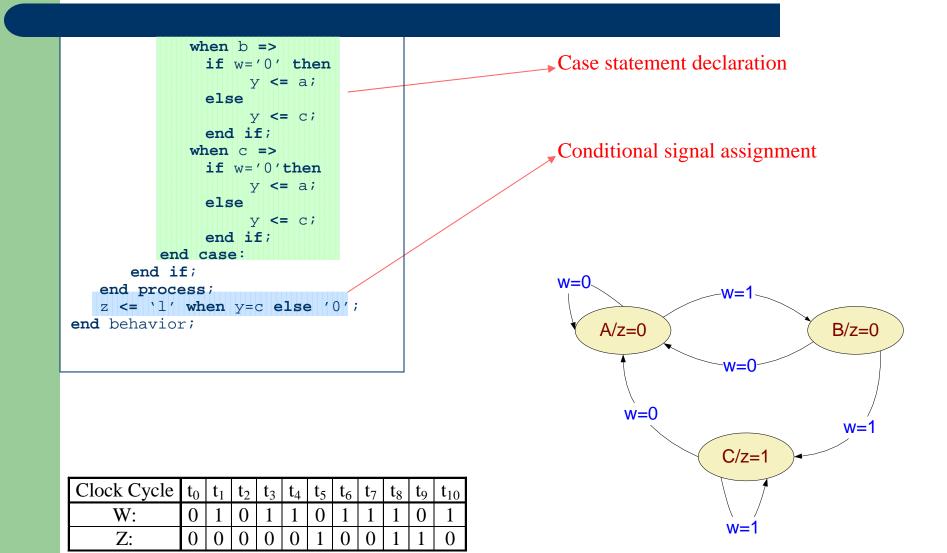

### **A Secuence Detector (continued)**

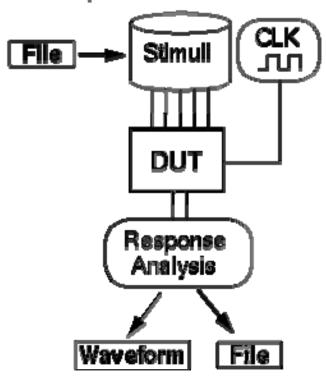

#### **Testbenches**

- Stimuli transmitter to DUT (testvectors)

- Needs not to be synthesizable

- No ports to the outside

- Environment for DUT

- Verification and validation of the design

- Several output methods

- Several input methods

#### Example of a testbench

### **Example Testbench**

entity TB\_TEST is end TB\_TEST; architecture BEH of TB\_TEST is -- component declaration of the DUT -- internal signal definition begin -- component instantiation of the DUT -- clock generation -- stimuli generation end BEH;

#### **Example Testbench**

```

entity TB_TEST is

end TB TEST;

architecture BEH of TB_TEST is

component TEST

port(CLK

: in std_logic;

RESET : in std_logic;

: in integer range 0 to 15;

Α

В

: in std_logic;

С

: out integer range 0 to 15);

end component;

constant PERIOD : time := 10 ns;

signal W_CLK : std_logic := '0';

signal W_A, W_C : integer range 0 to 15;

signal W_B

: std_logic;

signal W_RESET : std_logic;

begin

DUT: TEST

port map(CLK

=> W CLK,

RESET => W RESET,

=> W A,

Α

В

=> W B,

С

=> W_C);

. . .

```

# **Questions?**