# Introduction to VHDL

Yvonne Avilés Colaboration: Irvin Ortiz Flores Rapid System Prototyping Laboratory (RASP) University of Puerto Rico at Mayaguez

## What is VHDL?

- Very High Speed Integrated Circuit Hardware Description Language

- A programming language designed and optimized for describing the behavior of digital systems.

- Allows for automatic circuit synthesis and system simulation.

- A standard in the electronic design community.

- IEEE Standard 1076 defines the complete VHDL language

- The IEEE 1076-1987 and IEEE 1164 standards together form the complete VHDL standard in widest use today

### Entities and Architectures

- Every VHDL design description consists of at least one entity/architecture pair.

- A VHDL entity is a statement that defines the external specification of a circuit or sub-circuit.

- Provides the complete interface for a circuit

- Names, data types, direction of ports

```

entity compare is

port( A, B: in bit_vector(0 to 7);

EQ: out bit);

end compare;

```

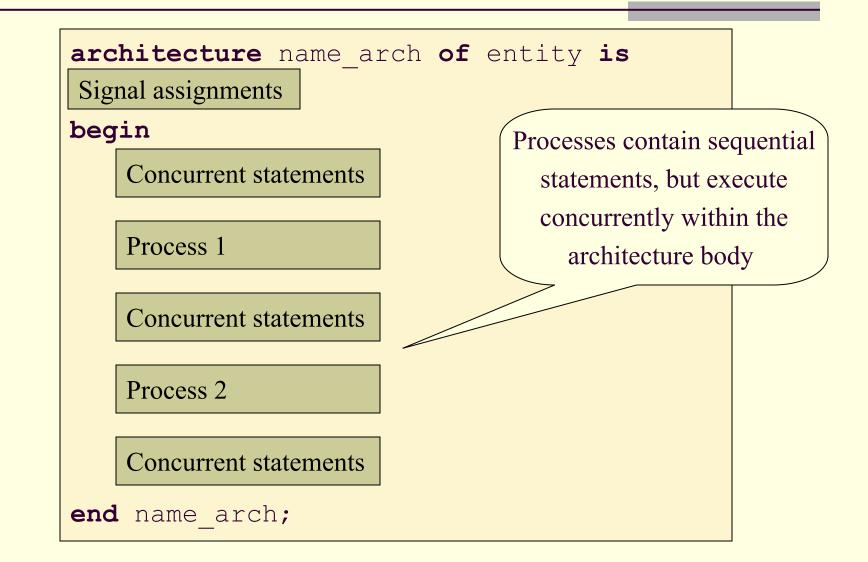

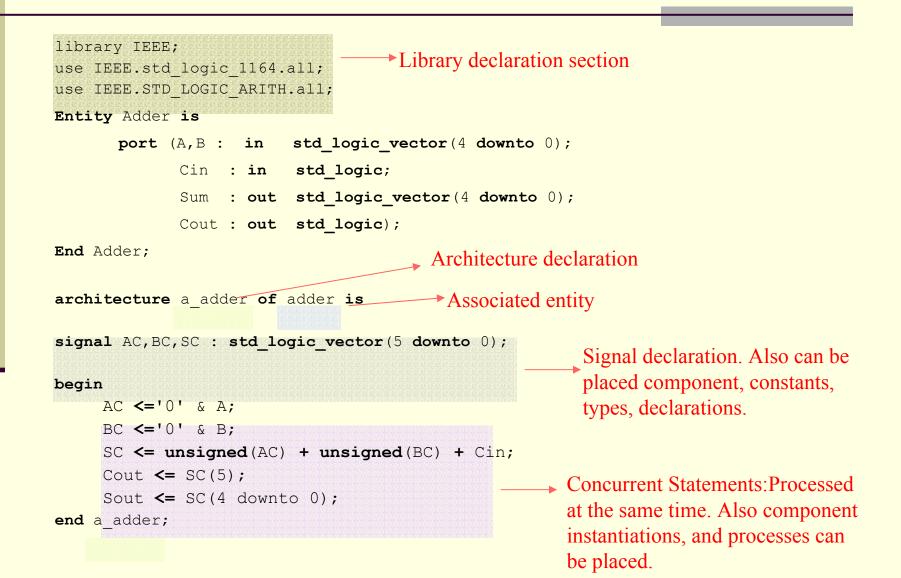

### Architecture Declaration

- Every referenced entity in a VHDL design description must be bound with a corresponding architecture.

- The architecture describes the actual function—or contents—of the entity to which it is bound.

```

architecture compare1 of compare is begin

```

```

EQ <= '1' when (A = B) else '0';

```

```

end compare1;

```

- Hierarchy and subprogram features of the language allow lowerlevel components, subroutines and functions in architectures; a process allows complex registered sequential logic as well.

- VHDL allows more than one alternate architecture for an entity.

### VHDL Architecture Structure

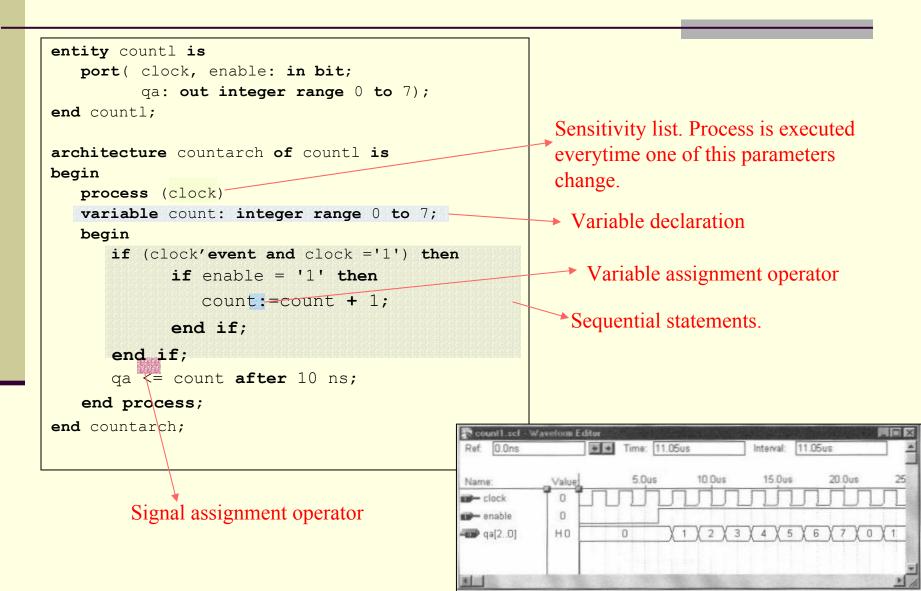

## VHDL Process Syntax

```

P1: process (<sensitivity list>)

<variable declarations>

begin

<sequential statements>

end process P1;

```

Within a process: Variables are assigned using := and are updated immediately. Signals are assigned using <= and are updated at the end of the process.</p>

## Signals Vs Variables

#### Signals

- Used to connect components or to carry information between processes

- When inside of a process, its value is updated when the process suspends

- Signal assignment operator: <=</p>

- Variables

- Local to a process

- Not visible outside the process

- Values are updated immediately after the assignment

- Variable assignment operator: :=

## Signals Vs Variables

#### Signals

- Initial values: A=5, X=10, B=15

- Final values: A=10, B=5

Sigproc:

process(A,X)

Begin

A <= X;

B <= A;

End process Sigproc;</pre>

```

Variables

Initial values: X=10

Final values: A=10,

B=10

Sigproc: process(X)

Variable A, B :

integer;

Begin

A := X;

B := A;

End process Sigproc;

```

### Data Types

Like a high-level software programming language, data is represented in terms of high-level data types.

Every data type in VHDL has a defined set of values and valid operations.

#### Data Type Values

#### Example

Bit **'1','0'** (array of bits) **Bit\_vector** Boolean True, False -2, -1, 0, 1, 2, 3, 4 . . . Integer Real 1.0, -1.0E5 Time 1 ua, 7 ns, 100 ps Character 'a', 'b', '2, '\$', etc. (Array of characters) String

```

Q<='1';

DataOut <= "00010101";

EQ <= True;

Count <= Count + 2;

V1 = V2 / 5.3

Q <= '1' after 6 ns;

CharData <= 'X';

Msg <= "MEM: " & Addr

```

## Design Units

- Entity : Interface

- Architecture : Implementation, behavior, function

- Configuration : Model chaining, structure, hierarchy

- Process : Concurrency, event controlled

- Package : Modular design, standard solution, data types, constants

- Library : Compilation, object code

## Levels of Abstraction

#### Behavior

- Relies on processes to implement sequential statements

- Dataflow

- Describe circuit in terms of how data moves through the system.

- Also referred to as register transfer logic, or RTL.

- Structure

- Used to describe a circuit in terms of its components

- Requires hierarchical constructs

- Mixed Method

- Any combination of methods

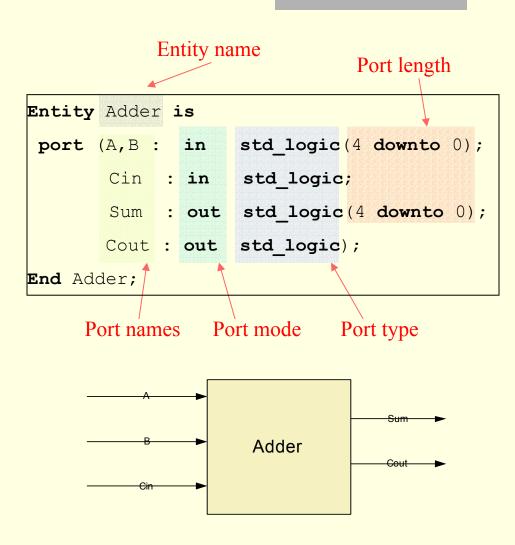

## **Entity Declaration**

- Specifies the unit's ports

- States the port's name type, mode

- Ports can be *in*, *out* or *inout*

- Port size can be from a bit to a bit vector

#### An Architecture Example

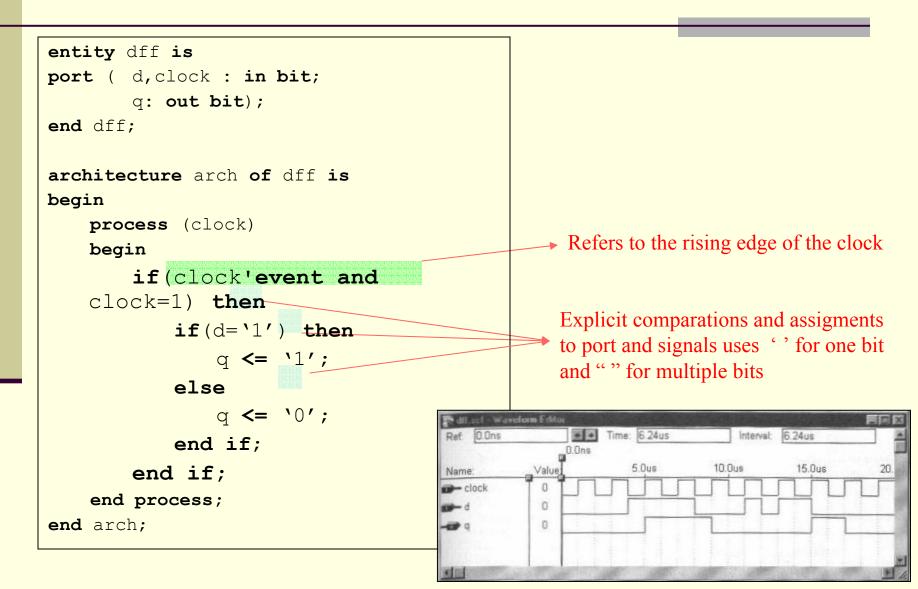

# A "D" Flip-Flop

## D Flip-Flop Behavioral

```

--Active low preset and clear inputs

entity dffpc2 is

port(d, clock, clrn, prn:in bit;

q,qbar:out bit;

end dffpc2;

architecture arch of dffpc2 is

begin

process(clock, clrn, prn)

begin

if(clock'event and clock =

'1') then

😰 dffpc2.scf - Waveform Editor

- 0 >

Time: 0.2ns

Ref: 370.0ns

+ +

Interval:

-369.8ns

q <= not prn or (clrn and

d);

200 Dns

300.0ns

Value:

100 Ons

Name:

- clock

gbar <= prn and (not clrn</pre>

cirn

or not d);

pm pm

1

end if;

0

d -

- 0 q

end process;

- gbar

0

end arch;

```

4

## D Flip-Flop Dataflow

```

--D flip-flop dataflow

--Includes preset and clear

entity dff flow is

port (d, prn, clrn: in bit;

q,qbar: out bit);

end dff flow;

architecture archl of dff flow is

begin

q <= not prn or (clrn and d);</pre>

gbar <= prn and (not clrn or not</pre>

d);

end arch1;

🐼 dff_flow.scf - Waveform Editor

• • Time: 108.0ns

Ref. 0.0ns

Interval:

0.0ns

50.0ns

100.0ns

Value

Name:

- cim

0

pm- pm

0

D-d

0

-00 0

```

- 0 ×

108.0ns

150.0ns

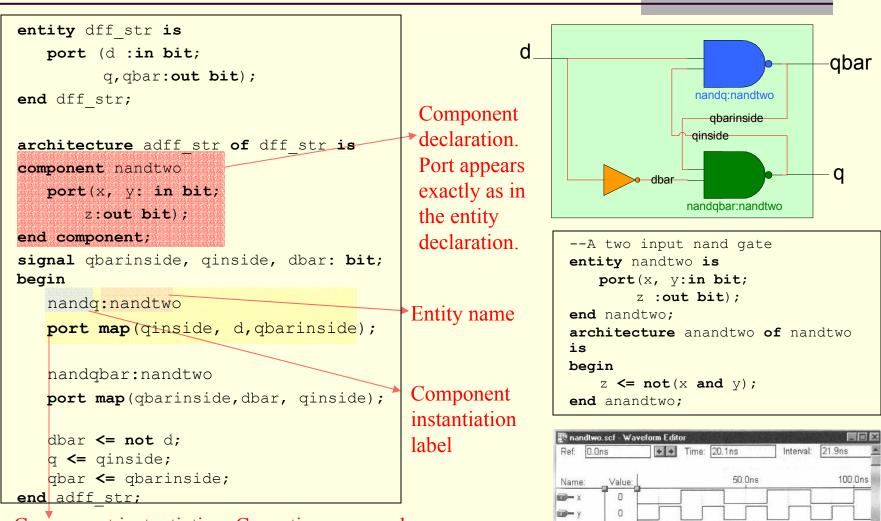

## D Flip-Flop Structural

- Z

4

1

Component instantiation. Conections are made by correspondence

## Three-Bit Binary Counter

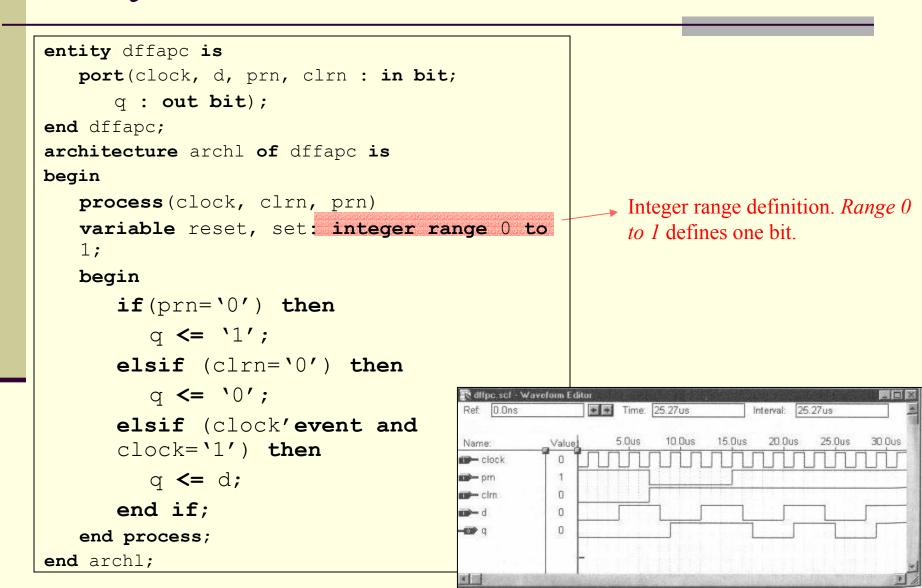

## D Flip-Flop with Asynchronous Preset and Clear

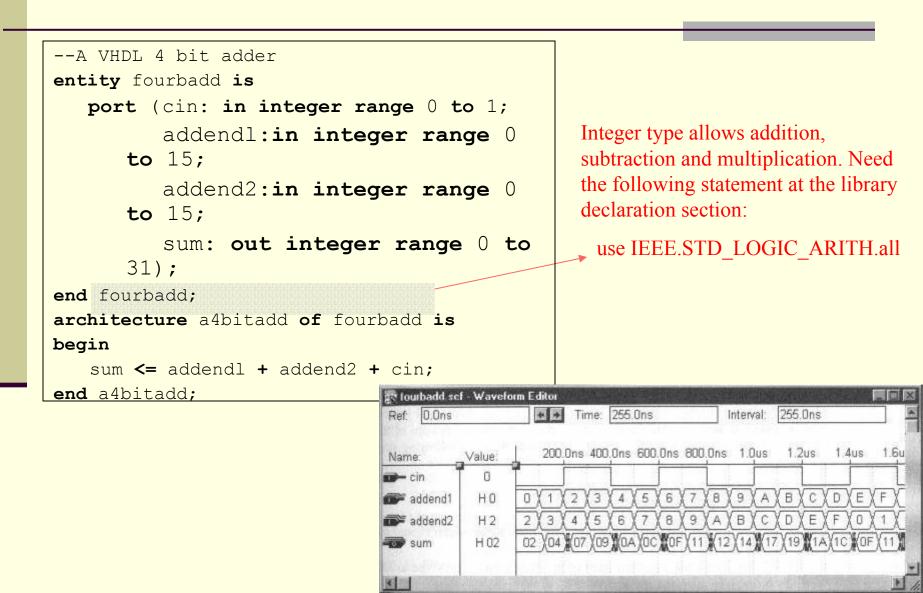

#### Four Bit Adder

## Synthesis

- Synthesis is a process of translating an abstract concept into a less-abstract form.

- The highest level of abstraction accepted by today's synthesis tools is the dataflow level.

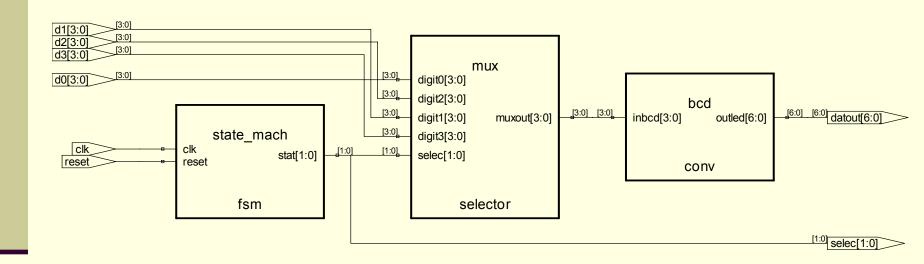

## Display Driver

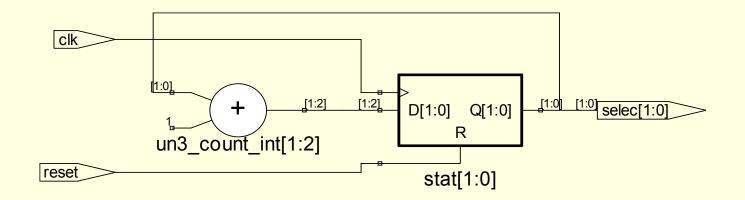

#### State Machine

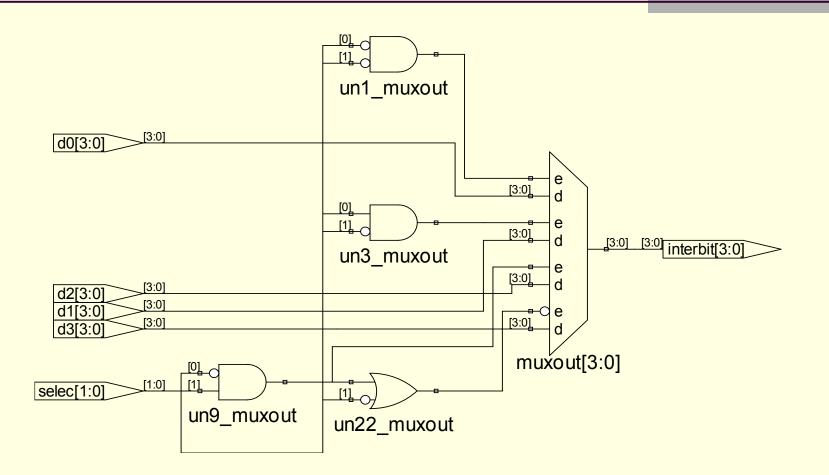

#### Data Selector

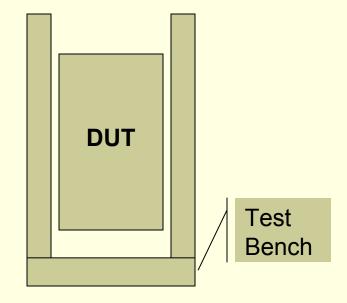

#### Test Benches

- VHDL can capture performance specification for a circuit, in the form of a test bench.

- Test benches are VHDL descriptions of circuit stimuli and corresponding expected outputs that verify the behavior of a circuit over time. Test benches should be an integral part of any VHDL project and should be created in tandem with other descriptions of the circuit.

### Link for VHDL Tutorial

http://www.aldec.com/Downloads/