Simulación Procesador RISC

INEL 4215

Agosto - 2003

Descripción general del proyecto

En el libro de texto del curso, “Computer Systems Design and Architecture” se describe la arquitectura de un procesador RISC sencillo (SRC por sus siglas en inglés). Este procesador se utiliza como ejemplo a través de todo el texto para describir características, funciones y aplicaciones de los procesadores.

Para comprender mejor el comportamiento de este procesador y varias de las consideraciones en su proceso de implementación, se requiere el diseño e implementación de un simulador para una versión simplificada del mismo.

Los/as estudiantes del curso formarán grupos de trabajo, para desarrollar, cada grupo, su versión del simulador. La descripción del simulador se muestra a continuación:

Memoria y Registros

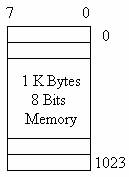

La memoria a la que puede acceder el procesador tiene un máximo de 1 KB organizado en 1024 localizaciones de 1 byte cada una.

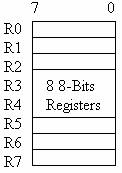

Internamente el procesador tiene 8 registros de propósito general de 8 bits cada uno. Los nombres de los registros van de r0 a r7.

En adición a estos registros el procesador posee un PC (program counter) de 10 bits y un IR (instruction register) de 24 bits. El formato del IR se muestra en la siguiente figura:

![]()

Op : Código de 5 bits que representa la acción (instrucción) que se ejecutará

ra: Tres bits que indican cuáles de los ocho

registros se utilizará como registro a

rb: Tres bits que indican cuáles de los ocho

registros se utilizará como registro b

rc: Tres bits que indican cuáles de los ocho

registros se utilizará como registro c

c: 10 bits que realizan la misma función que los campos c1, c2 y c3 del procesador

SRC mostrado en el texto

Descripción del set de instrucciones

La descripción del set de instrucciones del procesador se muestra en las secciones 2.3 a 2.5 del texto y en el apéndice B del libro. Un resumen del set de instrucciones del procesador se muestra en la siguiente tabla.

|

op |

nombre |

operandos |

operaciones |

Comentarios |

|

0 |

NOP |

|

Does nothing |

|

|

1 |

LD |

RA,RB,C |

If rb = 0 R[ra] = M[c] Else R[ra] = M[c+R[rb]] |

|

|

2 |

LDR |

RA,C |

R[ra] = M[pc + c] |

|

|

3 |

ST |

RA,RB,C |

If rb = 0 M[c2] = R[ra] Else M[c2+R[rb]] = R[ra] |

|

|

4 |

STR |

RA,C |

M[pc+c] = R[ra] |

|

|

5 |

LA |

RA,RB,C |

If rb = 0 R[ra] = c Else R[ra] = c + R[rb] |

|

|

6 |

LAR |

RA,C |

R[ra] = PC + c |

|

|

8 |

BR |

RB,RC,cond |

If cond is true PC = R[rb] |

Conditions 000 don’t jump 001 jump always 010 R[rc] = 0 011 R[rc] <> 0 100 R[rc] >= 0 101 R[rc] < 0 |

|

9 |

BRL |

RA,RB,RC,cond |

R[ra] = pc If cond is true PC = R[rb] |

Conditions are the same as above |

|

12 |

ADD |

RA,RB,RC |

R[ra] = R[rb] + R[rc] |

|

|

13 |

ADDI |

RA,RB,C |

R[ra] = R[rb] + c |

|

|

14 |

SUB |

RA,RB,RC |

R[ra] = R[rb] – R[rc] |

|

|

15 |

NEG |

RA,RC |

R[ra] = -R[rc] |

|

|

20 |

AND |

RA,RB,RC |

R[ra] = R[rb] ^ R[rc] |

|

|

21 |

ANDI |

RA,RB,C |

R[ra] = R[rb] ^ c |

|

|

22 |

OR |

RA,RB,RC |

R[ra] = R[rb] v R[rc] |

|

|

23 |

ORI |

RA,RB,C |

R[ra] = R[rb] v c |

|

|

24 |

NOT |

RA,RC |

R[ra] = |

|

|

26 |

SHR |

RA,RB,RC,count |

If count = 0 R[ra] = R[rb] shr R[rc] Else R[ra] = R[rb] shr count |

Only 5 lsb of RC are considered |

|

27 |

SHRA |

RA,RB,RC,count |

If count = 0 R[ra] = R[rb] shra R[rc] Else R[ra] = R[rb] shra count |

Only 5 lsb of RC are considered |

|

28 |

SHL |

RA,RB,RC,count |

If count = 0 R[ra] = R[rb] shl R[rc] Else R[ra] = R[rb] shl count |

Only 5 lsb of RC are considered |

|

29 |

SHC |

RA,RB,RC,count |

If count = 0 R[ra] = R[rb] shc R[rc] Else R[ra] = R[rb] shc count |

Only 5 lsb of RC are considered |

|

31 |

STOP |

|

Stop flag is set |

|

Las operaciones aritméticas que realiza el procesador utilizan el formato de complemento de dos para representar números con signos. El formato se utiliza además para calcular las localizaciones de memorias cuando se hace acceso a la misma.

Configuración del Sistema que contendrá al Procesador

El procesador operará en un sistema con 512 localizaciones de memoria RAM que ocupará las localizaciones 0 a la 511. Cuando el sistema arranca el procesador comienza a ejecutar la instrucción que se encuentre en los primeros tres bytes de memoria.

El sistema también contará con varios dispositivos de I/O conectados al procesador utilizando las siguientes localizaciones de memoria:

512: teclado

514: entrada paralela

516: salida paralela

520 – 523: despliegue hexadecimal

La información proveniente del teclado se entrará por el teclado de la computadora en donde se corra la simulación. La entrada y la salida paralela se simulará utilizando archivos secuenciales y el despliegue hexadecimal se presentará en la pantalla de la computadora. La siguiente figura muestra un ejemplo de una posible configuración para la interfaz del programa.

Requisitos del trabajo

Composición de los Grupos

Los grupos de trabajo deberán tener de tres a cuatro integrantes quienes re repartirán las tareas de la forma más equitativa posible, tomando en consideración las preferencias, destrezas y habilidades particulares de cada integrante.

El grupo debe presentar, como parte de su reporte, un documento en donde describa las responsabilidades y contribuciones de cada una las personas que integraron el grupo de trabajo.

Características del Simulador

El simulador debe implementar todo el set de instrucciones (en lenguaje de máquina) del procesador con sus respectivos modos de direccionamiento. El simulador correrá los programas que se encuentran en la memoria comenzando por la que se encuentre en la localización cero (PC = 0). El contenido de la memoria se podrá cargar de archivos almacenados en el disco duro o disquetes. El formato de los archivos será de una línea por cada instrucción/dato representada por seis dígitos hexadecimales. El simulador permitirá que los programas se puedan ejecutar completos de principio a fin o una instrucción a la vez. En adición, en todo momento se podrá ver el contenido de los registros (incluyendo el PC y el IR) y el estado de los dispositivos de I/O.. El programa debe permitir que se pueda ver el contenido de cualquier sección de memoria.

Los programas pueden utilizar una interfaz gráfica o de tipo texto y se pueden implementar en cualquier lenguaje de programación.

Reporte del trabajo

Mas adelante se informará la descripción del reporte y el metodo de evaluación.