No. 3-2

| Boolean Algebra                           |                                             |

|-------------------------------------------|---------------------------------------------|

| Commutative Laws:                         |                                             |

| a + b = b + a                             | a • b = b • a                               |

| Associative Laws:                         |                                             |

| (a+b)+c = a+(b+c)                         | (ab)c = a(bc)                               |

| Identities:                               |                                             |

| a + 0 = a                                 | a•0=0                                       |

| a• 1=a                                    | a + 1 = 1                                   |

| Distributive Laws:                        |                                             |

| $a + (b \bullet c) = (a+b) \bullet (b+c)$ | $a \cdot (b+c) = (a \cdot b) + (a \cdot c)$ |

| Boolean Algebra     |               |         |  |

|---------------------|---------------|---------|--|

| Complement:         |               |         |  |

| a + a = 1           | a • a = 0     |         |  |

| a + a = a           | a • a = a     |         |  |

| Theorems:           |               |         |  |

| a + ab = a          | ab + ab = b   |         |  |

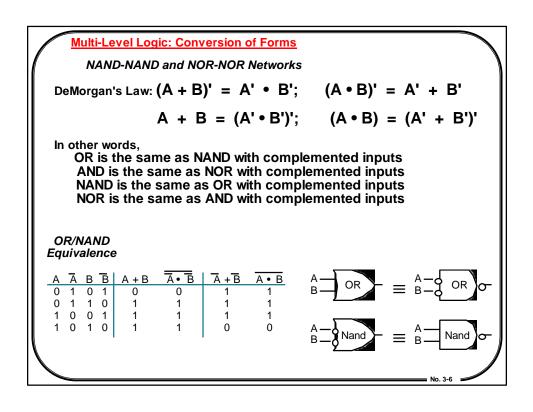

| DeMorgan's Theorem: |               |         |  |

| a • b = a + b       | a + b = a • b |         |  |

|                     |               | No. 3-4 |  |

## **Elements of a Data Sheet**

A data sheet contains all the relevant documentation that you need to use the component:

- 1. Description of Function

- 2. A function/truth table

- 3. A logic schematic with labeled I/Os

- 4. Boolean expression of function in terms of I/Os

- 5. Alternative package pint-outs

- 6. Internal transistor shcematics

- 7. Operating specifications

- 8. Recommended operating conditions

- 9. Electrical characteristics.

- 10. Switching characteristics.

<u>Operating Specifications</u>: the absolute worst-case conditions under which the component can operate or be stored. Max input volt: 7v, Temp: 0 to 70 C.

<u>Recommended Operating Conditions</u>: the normal operating conditions for the supply voltage, input voltages, output currents, and temperature.

$V_{HI}$ : min input volt recognized as a logic 1 (2v)

$V_{IL}$ : max input volt recognized as a logic 0 (0.8v)

**I**<sub>OH</sub>: max current gate can supply to maintain volt of logic 1 (-0.4 mA)

**I**<sub>OL</sub>: min current gate can supply to maintain volt of logic 0 (8 mA)

Electrical Characteristics: voltages and currents that can be observed at the inputs and outputs.

$V_{OH}$ : min output high volt (2.7v min, 3.4v typical)  $V_{OL}$ : max output low volt (0.4v max, 0.25v typical)

$I_{IH}$ : max current into input when high (20uA)  $I_{IL}$ : max current into input when low (-0.4 mA)

The voltages determine the **noise margin**: 0.7v margin on logic 1, and 0.4v on logic 0.

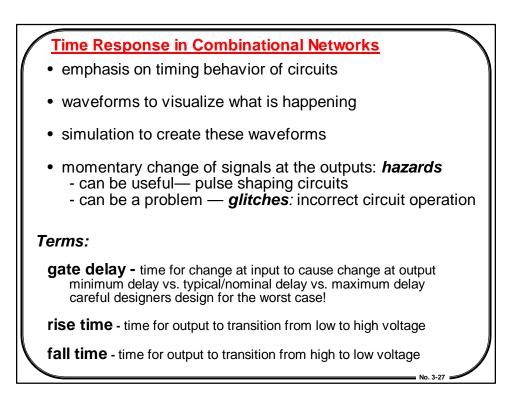

<u>Switching Characteristics</u>: the typical and maximum gatdelays under specified test conditions.

**t**<sub>PLH</sub>: delay from low to high (9ns typical, 15ns worst) **t**<sub>PHL</sub>: delay from high to low (10ns typical, 15ns worst)

<u>Fan-Out</u>: a given output can drive only a finite number of inputs before the output signal levels become degraded and are no longer recognized as good logic 1/0s.

To determine the **fan-out** examine the  $I_{OH}$  of the driving gate. This value must exceed the sum of the  $I_{IH}$  values of the inputs that the gate is driving.

Similarly, the  $I_{OL}$  of the gate must exceed the sum of the  $I_{IL}$  values of the inputs to which it is connected.

Example:  $I_{IH:}$  20uA,  $I_{OH:}$  -0.4mA  $I_{IL:}$  -0.4mA,  $I_{OL:}$  8mA

It can drive **20** gates to logic **1** and to logic **0**.

## **Technology Metrics**

There are differences in the underlying technologies that may make one technology more attractive than another. The main technology metrics are:

**1. Gate Delay**: the time delay between the changes. Om general, bipolar techs are faster than MOS (ECL the fastest).

**2. Degree of Integration**: the area required to implement a given function in the underlying tech. MOS pack much more densely than bipolar.

**SSI**: up to 10 gates

MSI: up to 100 gates (not important)

LSI / VLSI: up to 1000 gates (MOS has advantage)

**3. Power Dissipation**: the power consumption and heat generated that must be dissipated.

Bipolar generate more heat and consume more power

ECL consume the most power

MOS, especially CMOS, consume very little power **4. Noise Margin**: the max volt that can be added to or subtracted from the login voltages and still have the ckt interpret the voltage as the correct logic value.

Modern TTL / CMOS have good noise margins

ECL has tighter noise margin **5. Component Cost:** TTL, MOS, ECL