## 4. Current and Voltage Sources

## **Analog Design for CMOS VLSI Systems**

Franco Maloberti

## **Current mirrors**

A current mirror gives a replica (attenuated or amplified, if necessary) of a bias or signal current.

The most used current mirrors are:

- simple current mirror

- Wilson current mirror

- improved Wilson current mirror

- cascode current mirror

- modified cascode current mirror

- high compliance current mirror

- regulated cascode current mirror

## **Current mirrors**

A current mirror gives a replica (attenuated or amplified, if necessary) of a bias or signal current.

The most used current mirrors are:

- simple current mirror

- Wilson current mirror

- improved Wilson current mirror

- cascode current mirror

- modified cascode current mirror

- high compliance current mirror

- regulated cascode current mirror

## **Simple current mirror**

$$I_{Ref} = I_{1} = \frac{\mu C_{ox}}{2} \left(\frac{W}{L}\right)_{1} \left(V_{GS1} - V_{Th}\right)^{2} \left(1 + \lambda V_{DS1}\right)$$

$$I_{Out} = I_{2} = \frac{\mu C_{ox}}{2} \left(\frac{W}{L}\right)_{2} \left(V_{GS1} - V_{Th}\right)^{2} \left(1 + \lambda V_{DS2}\right)$$

$$V_{DS1} = V_{GS1} = V_{GS2}$$

to simplify the calculations let  $\lambda V_{DS1} = 0$

$$I_{Out} = I_{Ref} \frac{\left(\frac{W}{L}\right)_{2}}{\left(\frac{W}{L}\right)_{1}} \left(1 + \lambda V_{DS2}\right)$$

$$r_{out} = r_{ds2} = \frac{1}{\lambda I_{Out}}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

$$\frac{I_{Out}}{I_{Ref}} = \frac{\left(\mu C_{ox}\right)_2 \left(\frac{W}{L}\right)_2 \left(V_{GS} - V_{Th2}\right)^2 \left(1 + \lambda V_{DS2}\right)}{\left(\mu C_{ox}\right)_1 \left(\frac{W}{L}\right)_1 \left(V_{GS} - V_{Th1}\right)^2 \left(1 + \lambda V_{DS1}\right)}$$

Factors affecting the mirror accuracy:

- channel length modulation  $\frac{(1 + \lambda V_{DS2})}{(1 + \lambda V_{-1})}$

- offset between the threshold voltages

- imperfect geometrical matching

- technological parameter mismatch

- parasitic resistances

- Analog Design for CMOS VLSI Systems Franco Maloberti

$\mu C_{ox} \Big)_2$

## Accuracy:

$$\left(\frac{\delta I_{Out}}{I_{Out}}\right)^2 = \left(\frac{\delta W}{W}\right)^2 + \left(\frac{\delta L}{L}\right)^2 + \left(\frac{\delta C_{ox}}{C_{ox}}\right)^2 + \left(\frac{\delta \mu}{\mu}\right)^2 + 2\left(\frac{\delta V_{Th}}{V_{GS} - V_{Th}}\right)^2 + 2\left(\frac{\delta V_{GS}}{V_{GS} - V_{Th}}\right)^2$$

- The threshold mismatch is inversely proportional to the overdrive

- The threshold of the MOS transistors placed in close proximity are matches within few mV. By contrast, for MOS transistors which are hundred of microns apart have threshold voltages that can differ by few tens of mV.

- The last term refers to a mismatch in  $V_{GS}$ . It can derive from resistive voltage drop, due to a parasitic resistance in series with the source.

- The metal resistance is in the order of 20-50 mΩ/□, with 10 squares it result 0.2-0.5 Ω. If the current is 10 mA results an equivalent offset of 2-5 mV.

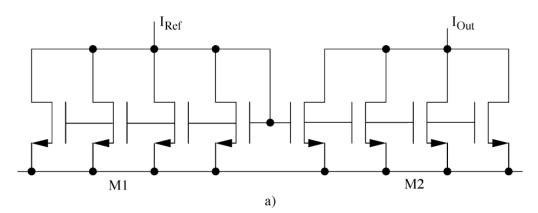

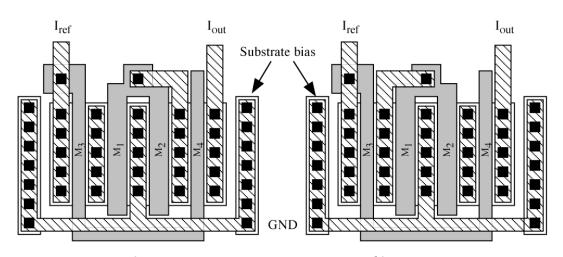

- $(\delta \mu / \mu)$  and  $(\delta C_{ox} / C_{ox})$  are minimized with closed and centroid common structures.

- ( $\delta W/W$ ) and ( $\delta L/L$ ) depends on the lithographic process.

For large W a good strategy is splitting the transistors into n equal parts connected in parallel.

$$\left(\frac{\delta I_{out}}{I_{out}}\right)^2 = \frac{1}{n} \left[ \left(\frac{\delta W}{W}\right)^2 + \left(\frac{\delta L}{L}\right)^2 \right] + K$$

Inter-digitized structures reduce parasitic capacitances.

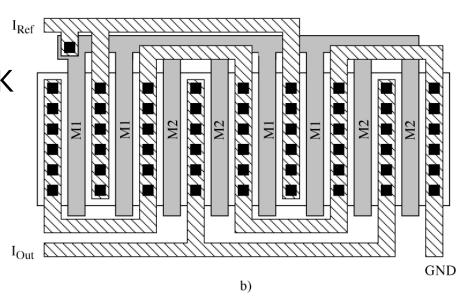

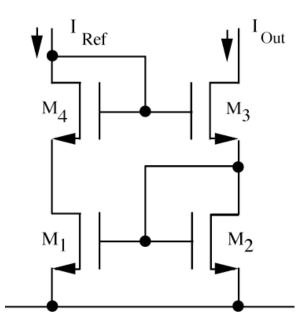

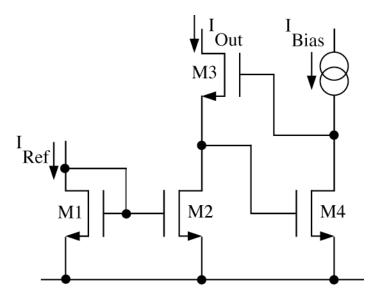

# $\underbrace{Wilson current mirror}_{G_3} g_{m3}V_{gs2}$

Increases the output resistance.

$$v_{g2} = v_{s3} = i_x / g_{m2} \quad v_{g3} = -g_{m1} v_{g2} r_T \quad r_T = r_{ds1} / / R_L$$

$$v_x = \frac{i_x}{g_{m2}} + (i_x - g_{m3} v_{gs3}) r_{ds3} \quad r_{out} = \frac{1}{g_{m2}} + \left[1 + \frac{g_{m3}}{g_{m2}} (1 + g_{m1} r_T)\right] r_{ds3}$$

•  $R_L$  must be large

I Ref

• there is a systematic error because  $V_{DS1} = V_{GS3} + V_{DS2}$

Analog Design for CMOS VLSI Systems Franco Maloberti

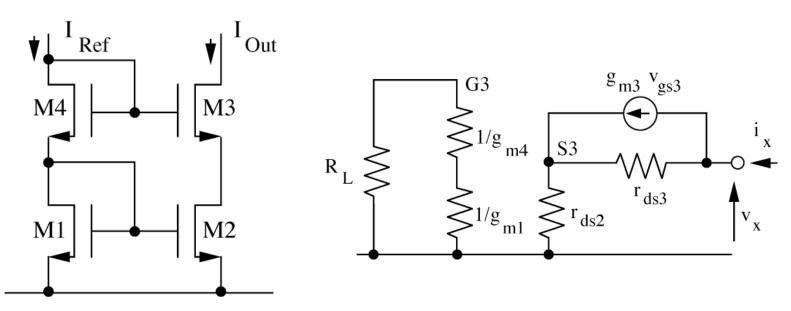

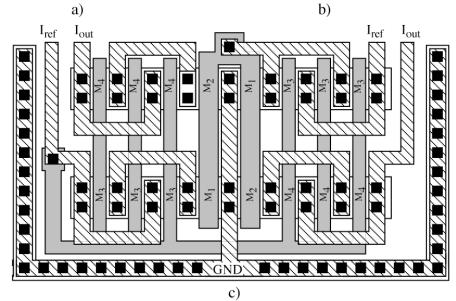

#### **Improved Wilson current mirror**

$$V_{DS1} = V_{GS3} + V_{DS2} - V_{GS4}$$

$$V_{DS1} = V_{DS2} \text{ if } V_{GS3} = V_{GS4}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

#### small signal analysis

$$V_{g3} = -g_{m1}V_{g2}r_{T}' \frac{R_{L}g_{m4}}{1 + R_{L}g_{m4}}$$

$$r_{T}' = r_{ds1} //(R_{L} + 1/g_{m4})$$

$$r_{T}' = r_{ds3} \frac{g_{m3}}{g_{m2}} g_{m1}V_{g2}r_{T}' \frac{R_{L}g_{m4}}{1 + R_{L}g_{m4}}$$

The output swing in the Wilson and improved Wilson schemes is limited to

$$V_{out,min} = V_{GS1} + V_{sat,3} = V_{Th,n} + V_{sat,1} + V_{sat,3}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

## Cascode current mirror

It increases the output resistance without feedback loop. It has the same resistance of the cascode load.

$$v_x = r_{ds2}i_x + r_{ds3} (1 + g_{m3} r_{ds2}) i_x$$

$r_{out} \approx r_{ds3} g_{m3} r_{ds2}$

The output swing is limited to

$$V_{G3} = V_{GS1} + V_{GS4} - V_{GS3}$$

$V_{out,min} = V_{S3} + V_{sat,3} \approx V_{Th} + 2V_{sat}$

Analog Design for CMOS VLSI Systems Franco Maloberti

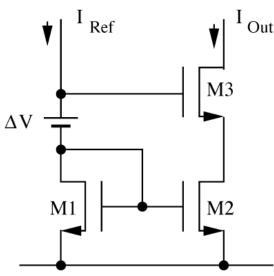

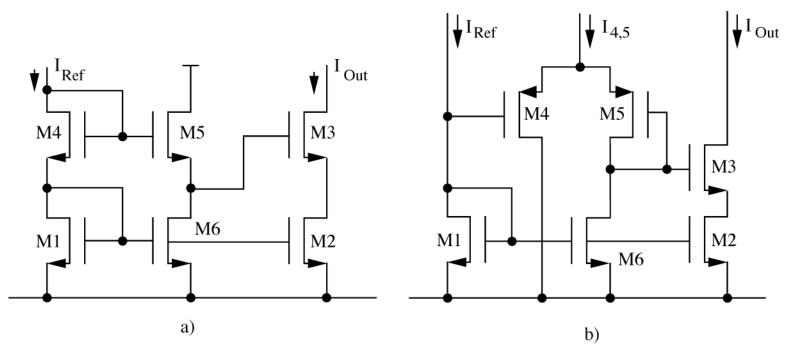

## Modified cascode current mirror

- The function of the transistor M4 is to shift the voltage V<sub>DS1</sub> of the amount enough to bias the gate of M3 without bringing M2 out of saturation.

- The use of M4 (matched with M3) allows to get  $V_{DS1} = V_{DS2}$  (this is paid with the output swing limitation).

- The output swing is improved by the use of a level shift  $V_{sat} < \Delta V < V_{Th}$ .

4. Current and Voltage Sources

The geometrical dimensions of M1, M6, M4, M5 determine, with  $V_{ov,4}$ ,  $\Delta V$ .

$$\Delta V = V_{GS4} - V_{GS5} = \sqrt{\frac{2I_4L_4}{\mu C_{ox}W_4}} - \sqrt{\frac{2I_5L_5}{\mu C_{ox}W_5}}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

Analog Design for CMOS VLSI Systems Franco Maloberti

## **Separate biasing in the cascode**

All transistors operate in saturation

$$I = I_{1} = I_{2} = I_{3} = I_{4} \text{ (current scaling is possible)}$$

$$\beta_{1} = \beta_{2} = \beta_{3} = \beta$$

$$V_{ov1} = V_{ov2} = V_{ov3} = V_{ov}$$

$$I_{4} = \beta_{4} (V_{ov4})^{2}; I_{2} = \beta (V_{ov})^{2}; I_{3} = \beta (V_{ov})^{2}$$

$$V_{DS2} = V_{ov}$$

$$V_{GS3} = V_{TH} + V_{ov}$$

$$V_{GS4} = V_{TH} + 2 V_{ov} \quad V_{ov4} = 2 V_{ov}$$

$$I_{ref} \downarrow I_{ref} \downarrow I_{ref}$$

$$M_{4} \downarrow I_{ref} \downarrow I_{out}$$

$$M_{4} \downarrow I_{out} \downarrow I_{out} \downarrow I_{out}$$

$$M_{4} \downarrow I_{out} \downarrow I_{out} \downarrow I_{out} \downarrow I_{out}$$

$$M_{4} \downarrow I_{out} \downarrow I_{out}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

<sup>4.</sup> Current and Voltage Sources

Current gain:

- systematic error due to  $V_{DS1} \neq V_{DS2}$

- systematic error due to body effect on M3

- output swing  $V_{out, min} = 2 V_{DSsat}$

- output impedance:  $r_{out} = r_{out4} g_{m2} r_{out2}$

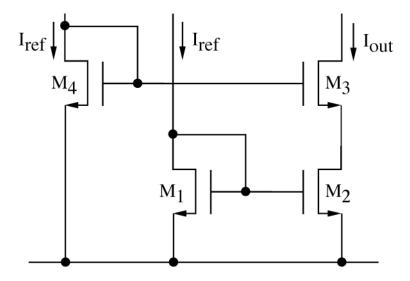

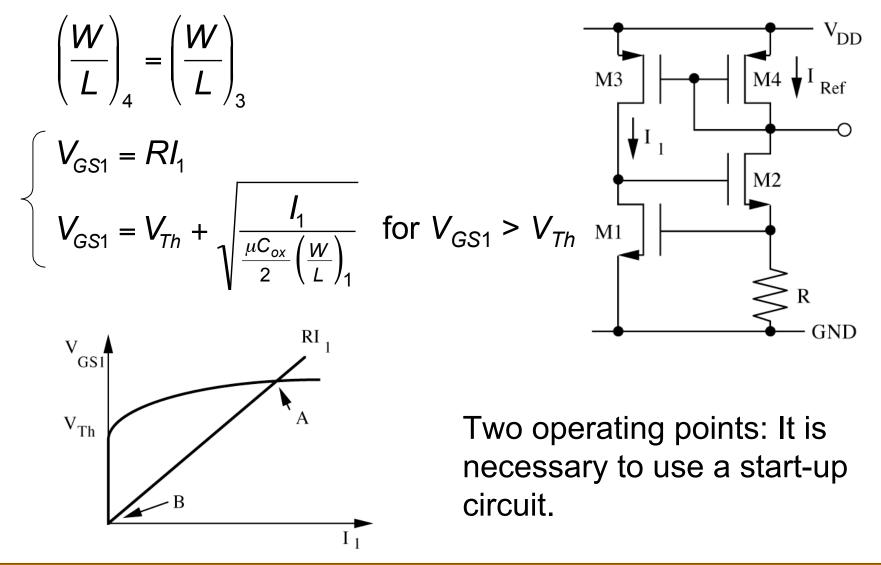

## High-compliance current mirror

M1 = M2; M3 = M4 therefore  $I_{out} = I_{ref}$ To properly work, we must impose  $V_{DSsatM4} < V_{Th1}$

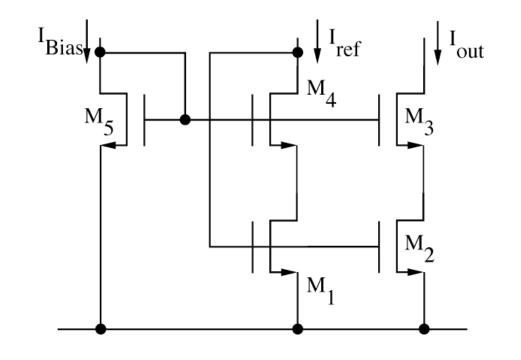

## **Regulated-cascode current mirror**

• Output impedance:

$$R_{out} = (g_{m3}r_{out3})r_{out2}(g_{m4}r_{out4})$$

• Output swing:

$$V_{outmin} = V_{GS4} + V_{DSsat3} \approx V_{Th} + 2 V_{sat}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

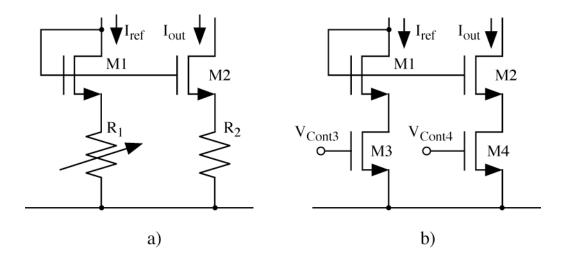

## Adjustable current mirror

- Degeneration resistances achieved with MOS transistors in the triode region.

- The voltages at the gates of M3 and M4 control the mirror factor.

## **Current references**

Most of the analog blocks require a reference current. These simple current references depend on supply.

The current accuracy is:

$$\left(\frac{\delta I_{Ref}}{I_{Ref}}\right)^{2} = \left(\frac{\delta \left(V_{DD} - V_{GS1}\right)}{V_{DD} - V_{GS1}}\right)^{2} + \left(\frac{\delta R_{L}}{R_{L}}\right)^{2}$$

The global inaccuracy is around ±32%.

The dependence on supply is critical when supply lines are affected by spur signals.

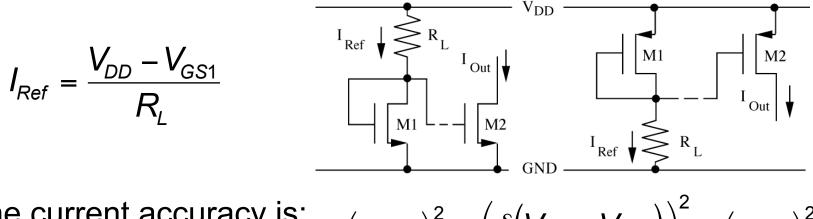

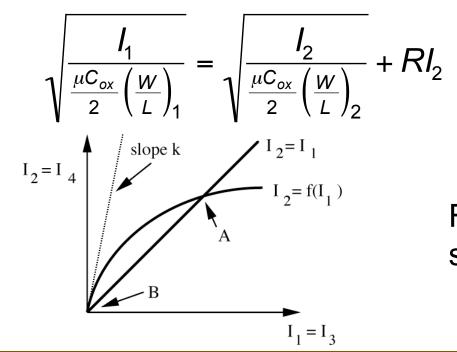

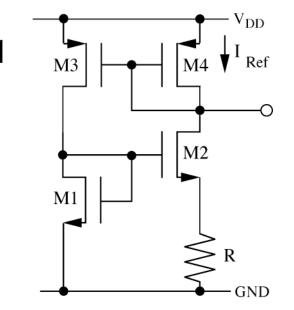

## Self biased (or bootstrapped) current reference

Analog Design for CMOS VLSI Systems Franco Maloberti

Self biased micro-current generator

$$\left(\frac{W}{L}\right)_{4} = \left(\frac{W}{L}\right)_{3} \quad \left(\frac{W}{L}\right)_{2} = k\left(\frac{W}{L}\right)_{1} \quad k > 0$$

• Assume M3 = M4 ideal mirror  $I_3 = I_4$

• Assume

$$V_{Th1} = V_{Th2}$$

For k = 10,  $V_R \approx 60$  mV, so R = 60 k $\Omega$  for I = 1 µA.

Analog Design for CMOS VLSI Systems Franco Maloberti

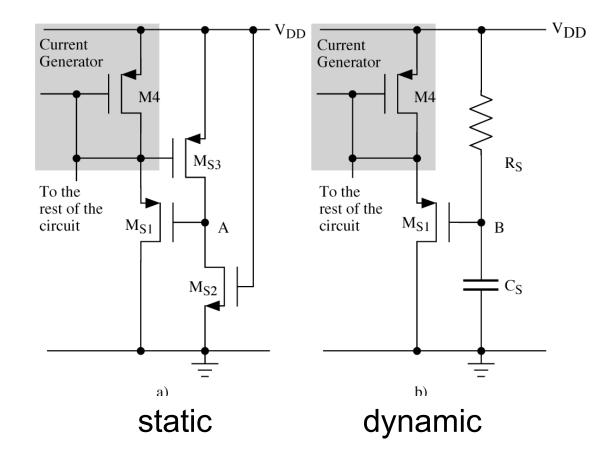

## **Start-up circuit**

Monitor if the current is zero and inject a current that starts the circuit.

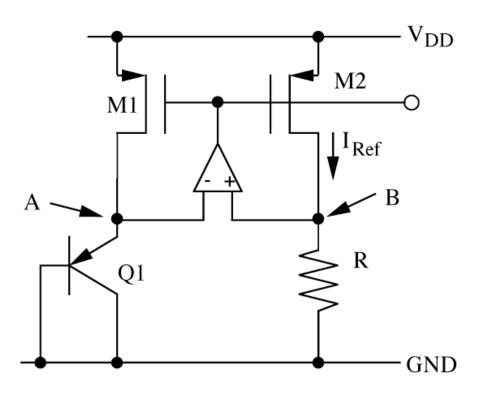

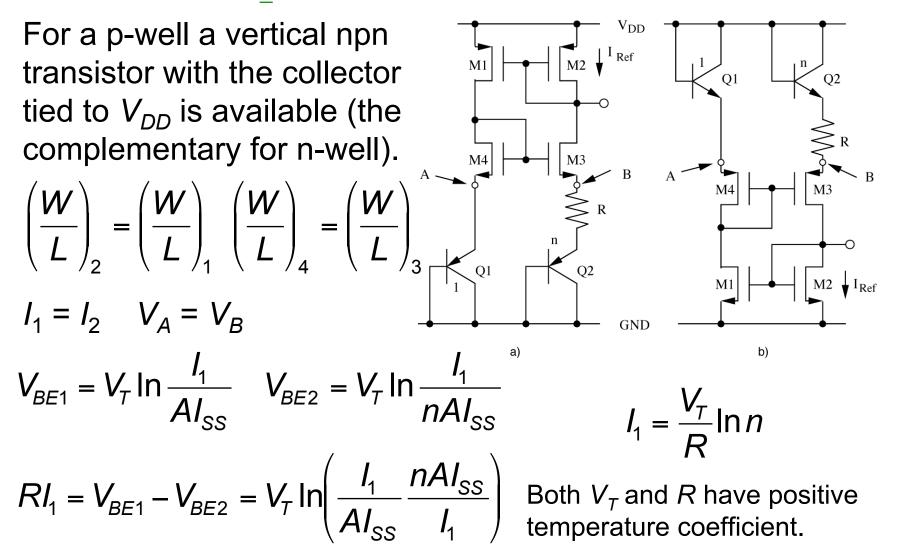

**V**<sub>BE</sub>-based current generator

The voltage across the resistance and the diode voltage are made equal by the feedback loop action.

## V<sub>7</sub>-based current generator

Analog Design for CMOS VLSI Systems Franco Maloberti

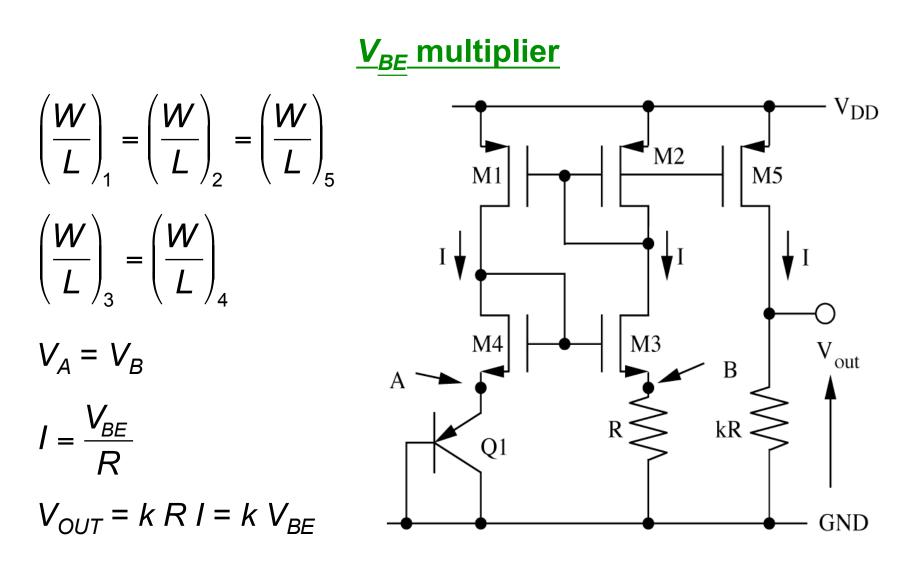

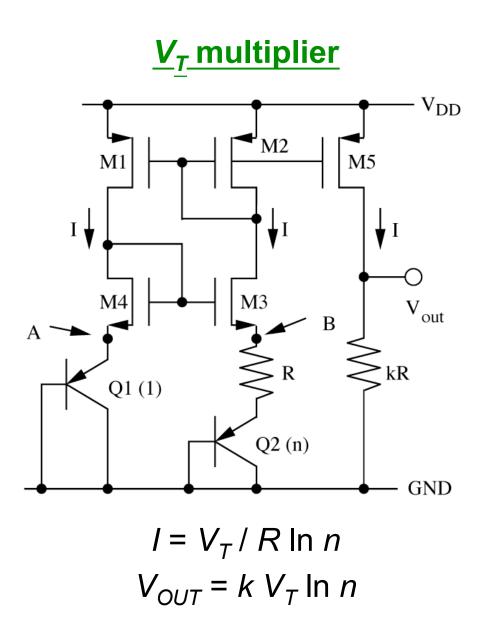

## **Voltage references**

- V<sub>BE</sub> multiplier

- V<sub>T</sub> multiplier

- Threshold voltage difference

- Band-gap

$V_{OUT}$  has a negative temperature coefficient

Analog Design for CMOS VLSI Systems Franco Maloberti

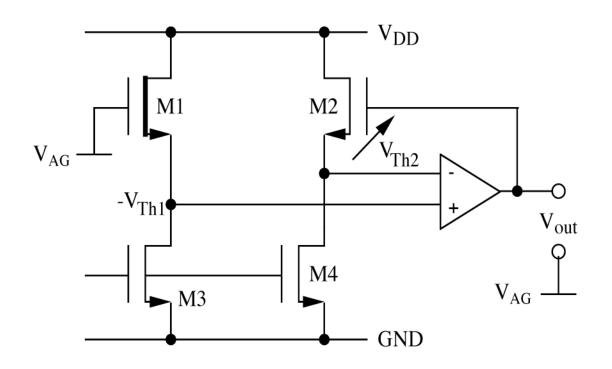

**Threshold voltage difference**

M1 and M2 have different threshold (enhancement and depletion or enhancement and enhancement)

$$V_{OUT} = -V_{Th1} + V_{Th2}$$

Analog Design for CMOS VLSI Systems Franco Maloberti

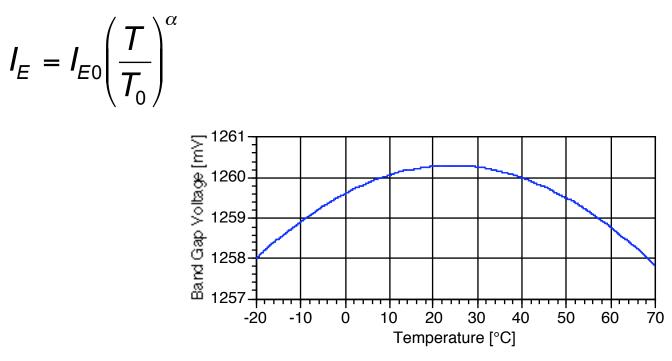

## **Band-gap reference voltage**

To obtain a reference voltage with zero temperature coefficient (in a defined temperature range) it is necessary to have:

$$V_{BG} = V_{BE} + m V_T$$

- V<sub>BE</sub> has negative temperature coefficient (- 2.2 mV/°C at 300 K)

- V<sub>T</sub> has positive temperature coefficient (+ 0.086 mV/°C at 300 K)

*m* ≈ 25.6

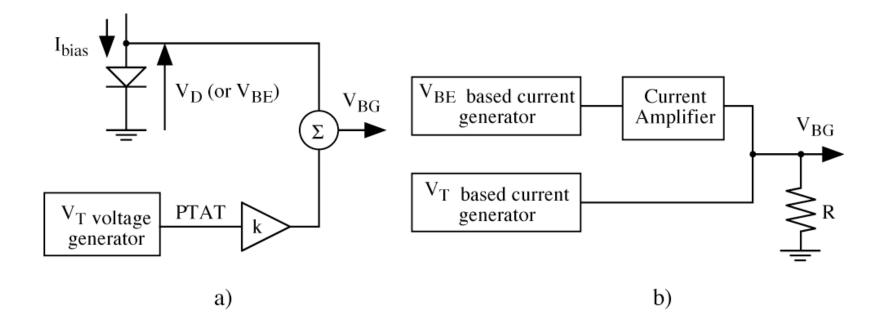

## Band-gap idea

a) implementation adding voltagesb) implementation adding currents and transforming current into voltage

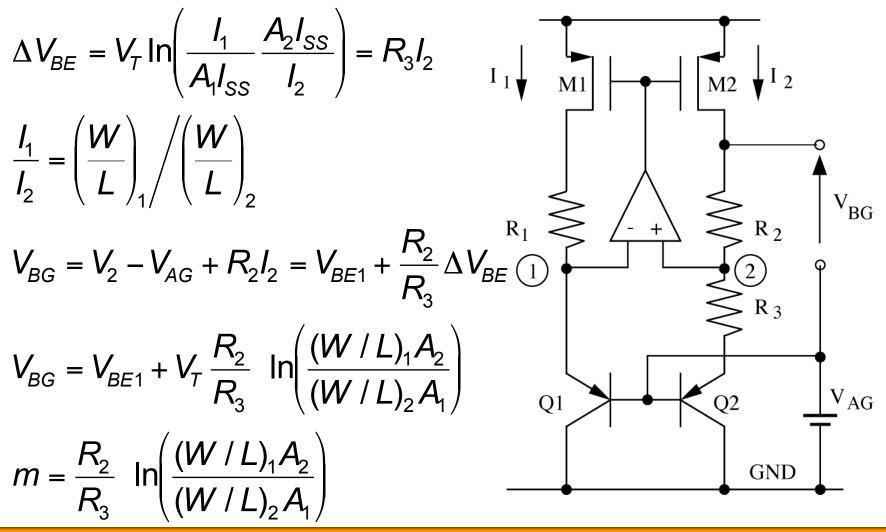

## Band-gap based on voltage processing

p-well process

Analog Design for CMOS VLSI Systems Franco Maloberti

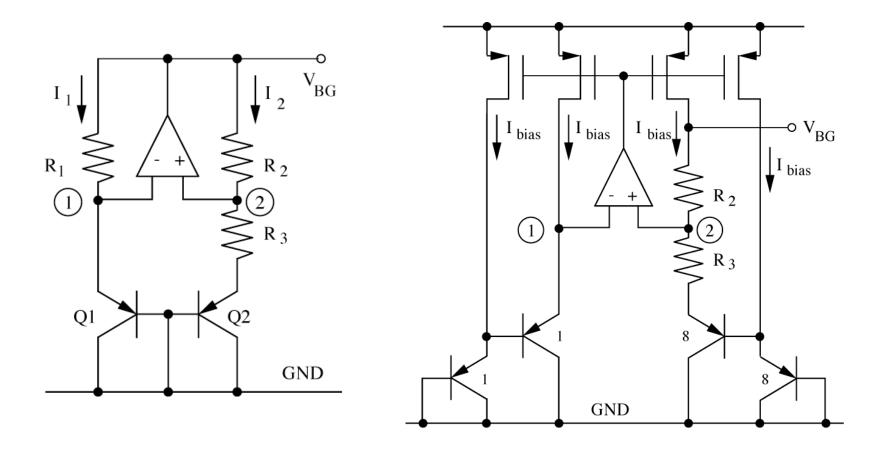

## **Other solutions**

current provided by the op-amp

double band-gap

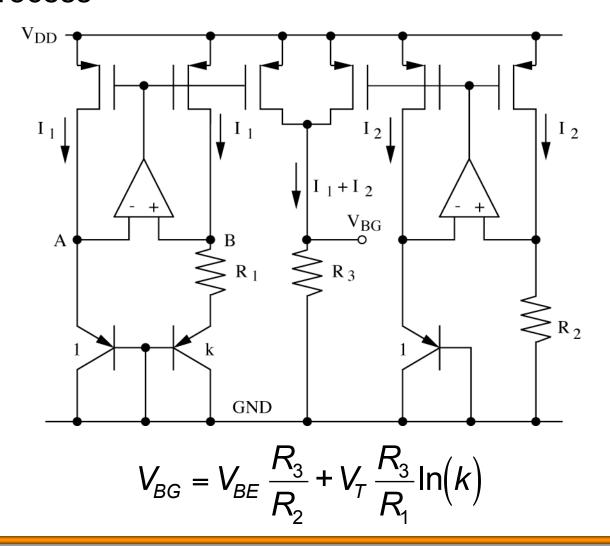

## Band-gap based on current processing p-well process

Analog Design for CMOS VLSI Systems Franco Maloberti

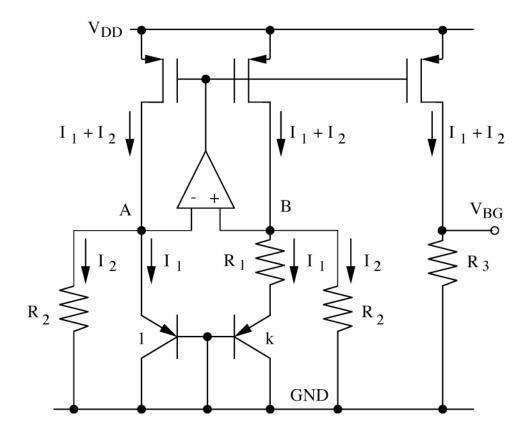

#### **Combining the two op-amps**

#### **Curvature error**

$$V_{BG} = V_G(T) - \left[V_G(T_0) - V_{BE}(T_0)\right] \frac{T}{T_0} - \left(\eta - \alpha\right) V_T \ln \frac{T}{T_0}$$

$\eta$  is a process dependent parameter whose value ranges from 3 to 4

Analog Design for CMOS VLSI Systems Franco Maloberti

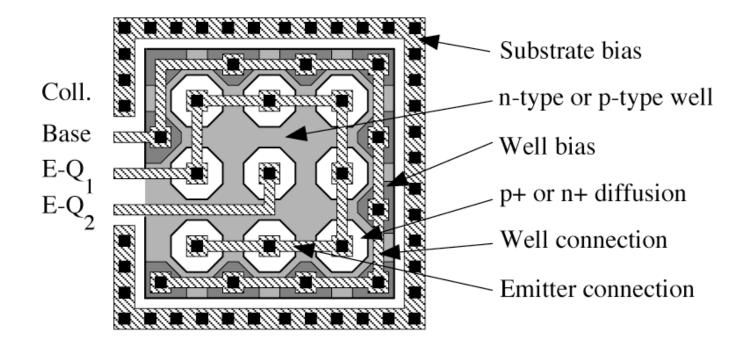

## Layout of a 8+1 BJT

- common centroid arrangement

- common well (same base voltage)