### Last Lecture -> CMOS Transistor

nMOS pMOS gate gate bulk drain source drain substrate source n+  $p^+$  $p^+$ n<sup>+</sup> n<sup>+</sup>  $p^+$ n-well p<sup>+</sup>-substrate

#

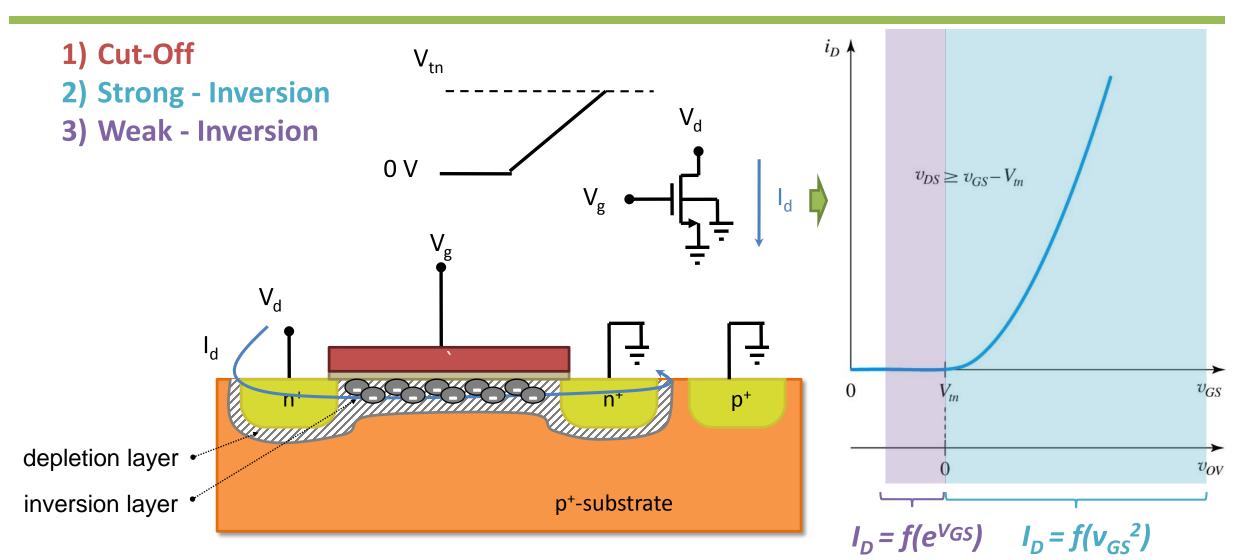

## Last Lecture — Strong Inversion

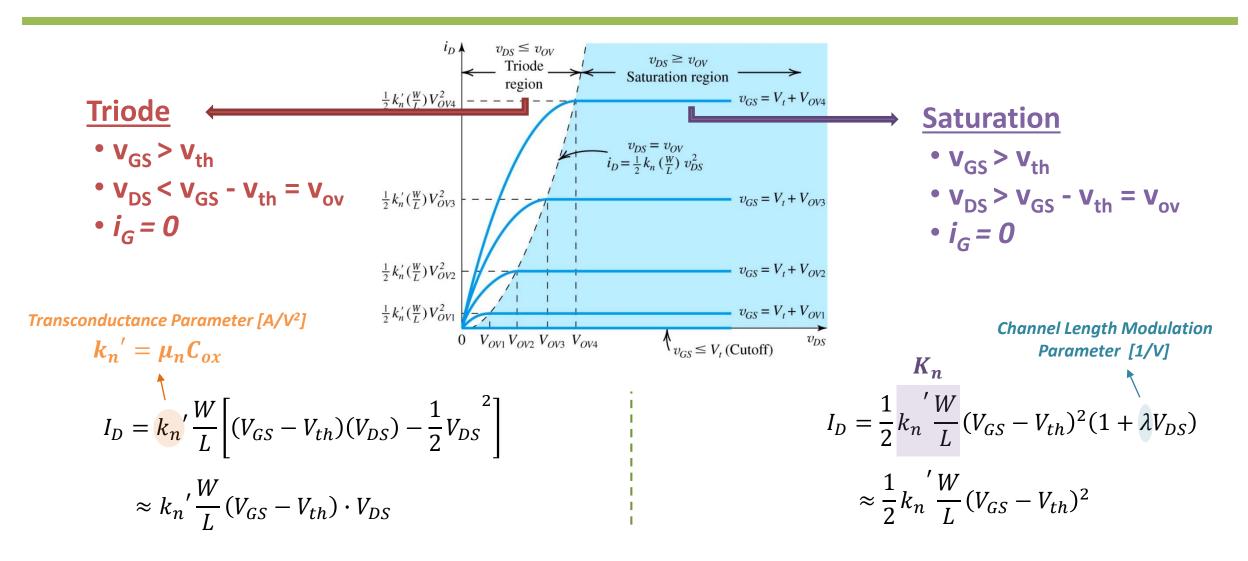

## nMOS Large Signal Model

10/28/2019

• Strong Inversion – Ohmic

$$I_D = \mu C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right] \qquad \qquad V_{GS} > V_{th} \\ V_{DS} < V_{OV}$$

• Strong Inversion - Saturation

$$I_D = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2 (1 + \lambda V_{DS}) \qquad \qquad V_{GS} > V_{th} \\ V_{DS} > V_{OV}$$

Weak Inversion - Saturation

$$I_D = I_0 \cdot e^{\frac{V_{GS} - V_{th}}{nU_T}}$$

$V_{th}$ -5· $U_T$  <  $V_{GS}$  <  $V_{th}$ -2 ·  $U_T$

Condition

# **MOSFET Model Parameters**

$U_t = kT/q \rightarrow thermal voltage (~25mV @ room temp.)$

- $\mu$   $\kappa_{s} = 1/n$   $C_{ox} = \epsilon_{ox}/t_{ox}$   $\epsilon_{ox}$  $t_{ox}$

- → electron/hole mobility

- $\kappa_s = 1/n \rightarrow \text{subthreshold slope coefficient (unit-less)}$

- $C_{ox} = \epsilon_{ox}/t_{ox} \rightarrow$  gate oxide capacitance per unit area (F/cm<sup>2</sup>)

- $\epsilon_{ox} \rightarrow dielectric permittivity of SiO_2$

- $\rightarrow$  oxide thickness

$K_n = k_n' W/L$  $k_n' = \mu C_{ox}$  $\gamma$

- $K_n = k_n' W/L \rightarrow transconductance parameter(A/V<sup>2</sup>)$

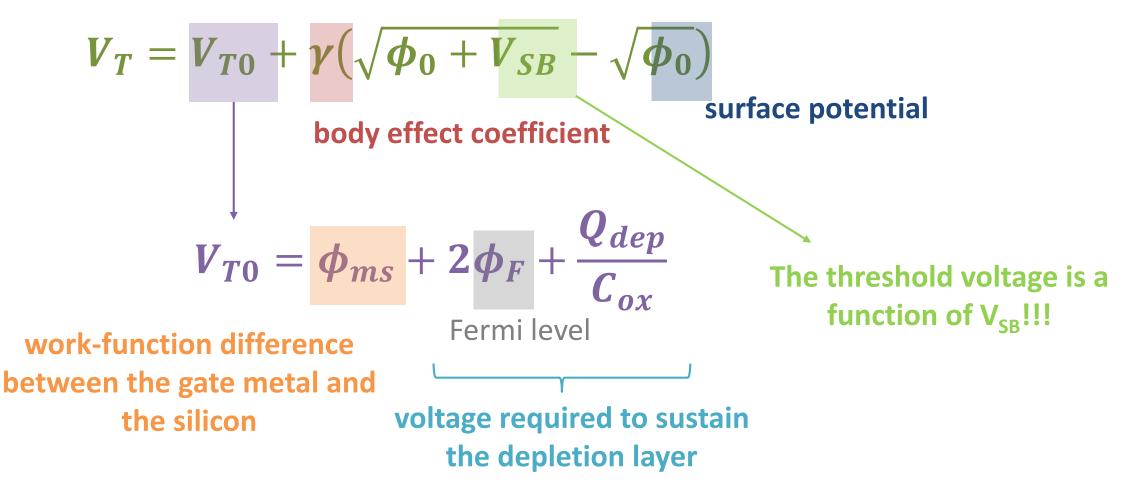

- $\rightarrow$  body effect coefficient (V<sup>1/2</sup>)

- → channel-length modulation parameter (V<sup>-1</sup>)

ν<sub>τ0</sub> ν<sub>τ</sub> φ<sub>0</sub>

λ

- $\rightarrow$  threshold voltage at V<sub>SB</sub>=0 (V)

- → threshold voltage (V)

- $\rightarrow$  ≈ surface potential (V)

# Weak Inversion vs Strong Inversion?

| Weak Inversion                                       | Strong Inversion                                    |

|------------------------------------------------------|-----------------------------------------------------|

| Saturation current is exponential in V <sub>GS</sub> | Saturation current is square law in V <sub>GS</sub> |

| V <sub>DSAT</sub> is constant at approximately 100mV | V <sub>DSAT</sub> varies linearly with gate voltage |

| Current flows by diffusion                           | Current flows mainly by drift                       |

| Charge concentrations are small                      | Charge concentrations are large                     |

| Currents are small                                   | Current are large                                   |

| Good for ultra-low-power operation                   | Good for high-power operation                       |

| Power efficiency is constant with current            | Power efficiency is lower                           |

| High noise and offset                                | Low noise and offset                                |

| Can work on low power supply voltage                 | Needs higher power supply voltages                  |

| Linearity is hard to achieve                         | Linearity is easy to achieve                        |

| Suited for slow-and-parallel architectures           | Suited for fast-and-serial architectures            |

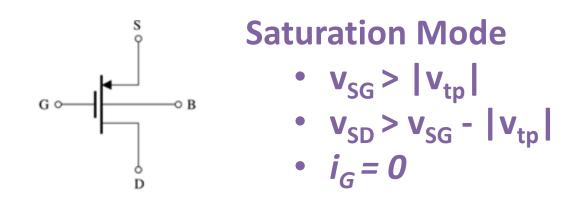

## pMOS Large Signal Model

10/28/2019

$V_{ov} = V_{SG} - |V_{tp}|$

#### **Ohmic Mode**

- $\mathbf{v}_{SG} > |\mathbf{v}_{tp}|$

- $v_{SD} < v_{SG} |v_{tp}|$ • *i* - 0

$I_{D} = \frac{1}{2} k_{p} \frac{W}{L} (V_{SG} - |V_{tp}|)^{2} (1 + \lambda V_{SD})$

$$\approx \frac{1}{2} k_p' \frac{W}{L} \left( V_{SG} - \left| V_{tp} \right| \right)^2$$

$$I_D = k_p' \frac{W}{L} \left[ \left( V_{SG} - |V_{tp}| \right) (V_{SD}) - \frac{1}{2} V_{SD}^2 \right]$$

$$\approx k_p' \frac{W}{L} \left( V_{SG} - |V_{tp}| \right) \cdot V_{SD}$$

pMOS Transconductance Parameter [A/V<sup>2</sup>]

$k_p' = \mu_p C_{ox}$

## **Threshold Voltage**

10/28/2019

The required voltage to produce and inversion layer.

## Example 5.2

Consider an nMOS transistor fabricated in a 0.18µm process with L=0.18µm and W=2um. The process technology is specified to have  $C_{ox}$ =8.6fF/µm<sup>2</sup>, µ<sub>n</sub>=450cm<sup>2</sup>/V·s, and V<sub>th</sub>=0.5V.

- a) Find  $V_{GS}$  and  $V_{DS}$  that result in the MOSFET operating at the edge of saturation with  $I_D = 100 \mu A$ .

- b) If  $V_{GS}$  is kept constant, find  $V_{DS}$  that results in  $I_D = 50 \mu A$ .

- c) To investigate the use of the MOSFET as a linear amplifier, let it be operating in saturation with

- $V_{DS}$ =0.3V. Find the change in i<sub>D</sub> resulting from v<sub>GS</sub> changing from 0.7V by +0.01V and by -0.01V.

## Example 5.3

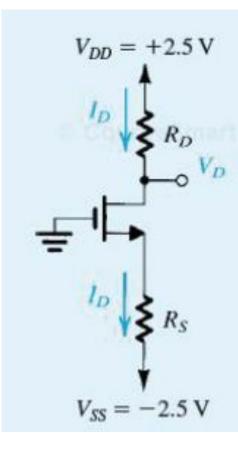

10/28/2019

Assuming  $\lambda$ =0, design the circuit below, that is, determine the values of R<sub>D</sub> and R<sub>S</sub>, so that the transistor operates at I<sub>D</sub>=0.4mA and V<sub>D</sub>=0.5V. The NMOS transistor has V<sub>th</sub>=0.7V,  $\mu_n C_{ox}$ =100 $\mu$ A/V<sup>2</sup>, and W/L=32.

## Example 5.5

An n-channel MOSFET operating with  $V_{ov}$ =0.5V exhibits a linear resistance  $r_{DS}$ =1k $\Omega$  when  $v_{DS}$  is very small.

- a) What is the value of the device trans-conductance parameter K<sub>n</sub>?

- b) Assuming  $\lambda = 0$ , what is the value of the current I<sub>D</sub> obtained when v<sub>DS</sub> is increased to 0.5V? And to 1V?

- c) Assuming an  $\lambda = 0.1V^{-1}$ , what is the value of the current  $I_D$  obtained when  $v_{DS}$  is increased to 0.5V? And to 1V?

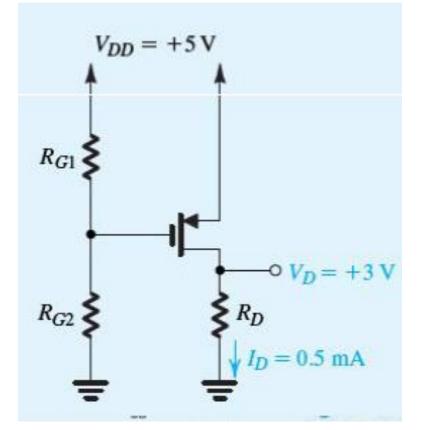

## Example 5.7

Assuming  $\lambda$ =0, design the circuit below, so that the transistor operates in saturation with I<sub>D</sub>=0.5mA and V<sub>D</sub>=3V. The PMOS transistor has V<sub>th</sub>=-1V, K<sub>p</sub>=1mA/V<sup>2</sup>. What is the largest value that R<sub>D</sub> can have while maintaining saturation-region operation?

# MOS Behavior → Intuitively

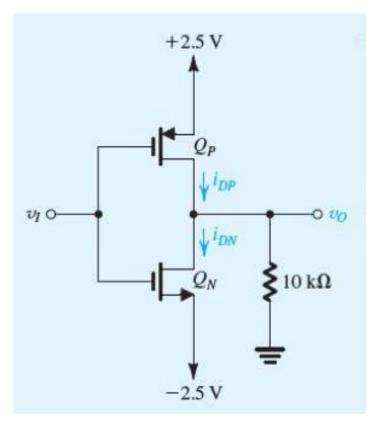

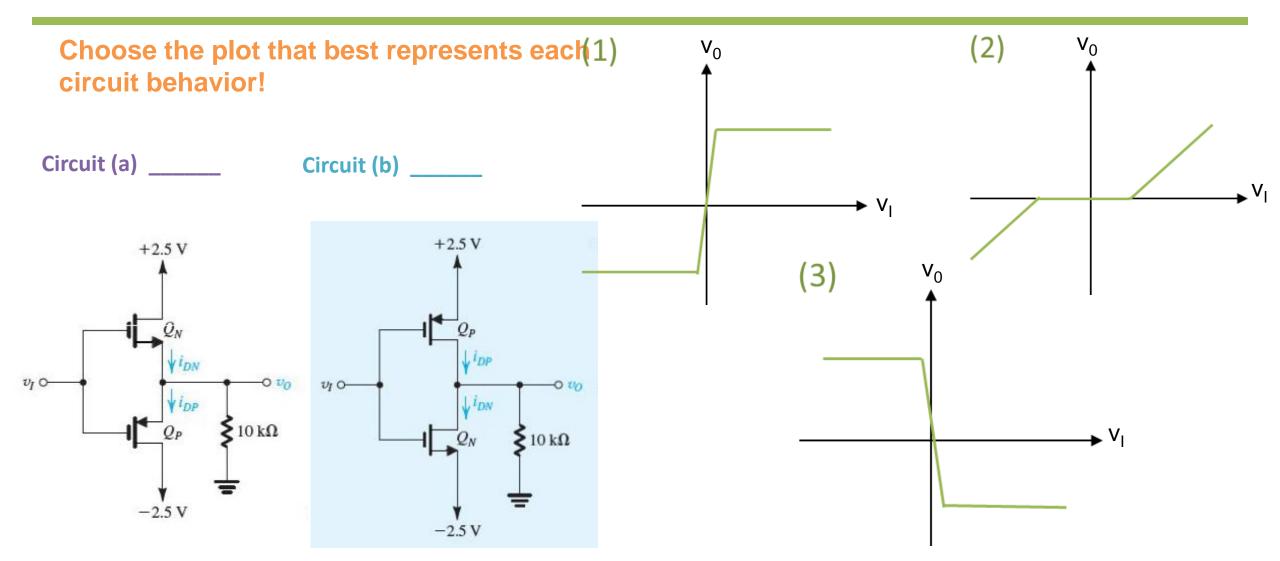

## Example 5.8

10/28/2019

14

Assuming matched NMOS and PMOS transistors with  $V_{thn}$ =- $V_{thp}$ =1V,  $K_n$ = $K_p$ =1mA/V<sup>2</sup> and  $\lambda$ =0, find the drain currents  $I_{Dn}$  and  $I_{Dp}$ , as well as the voltage  $v_o$ , for  $v_1$ =0V, +2.5V, and -2.5V.