## ARITHMETIC CIRCUITS

INEL 4205 - Ch. 4 - Set 1 Spring 2012

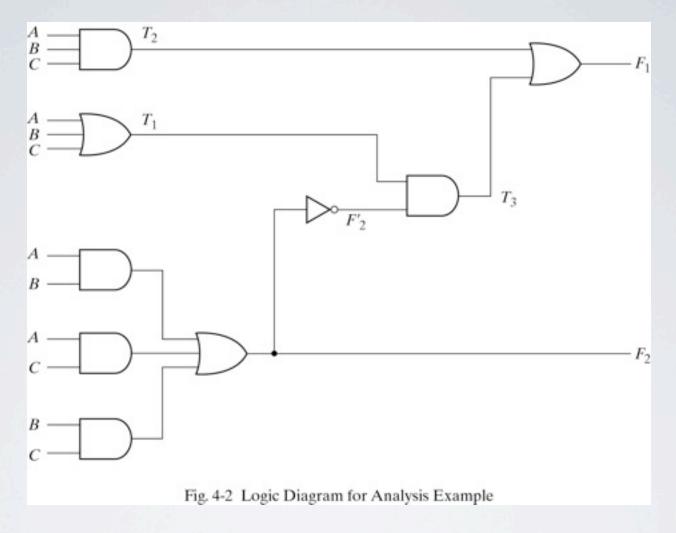

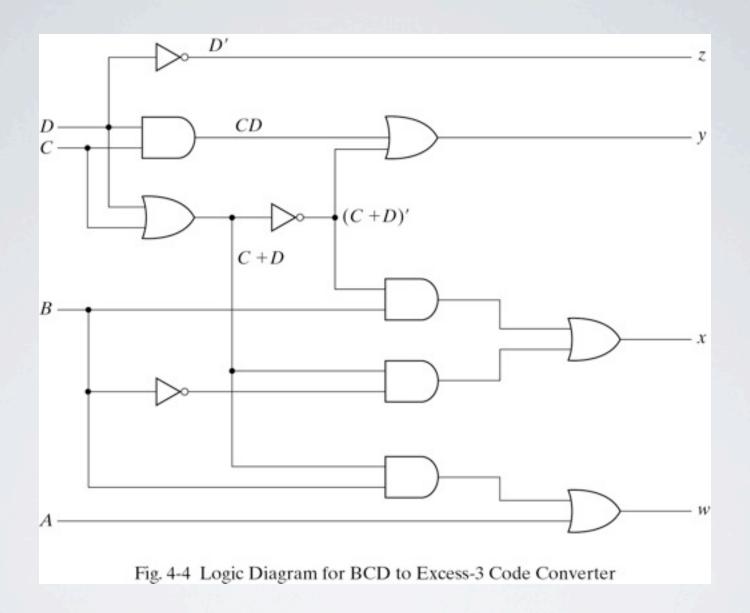

You can use intermediate variables to construct the boolean Functions from a complex logic diagram.

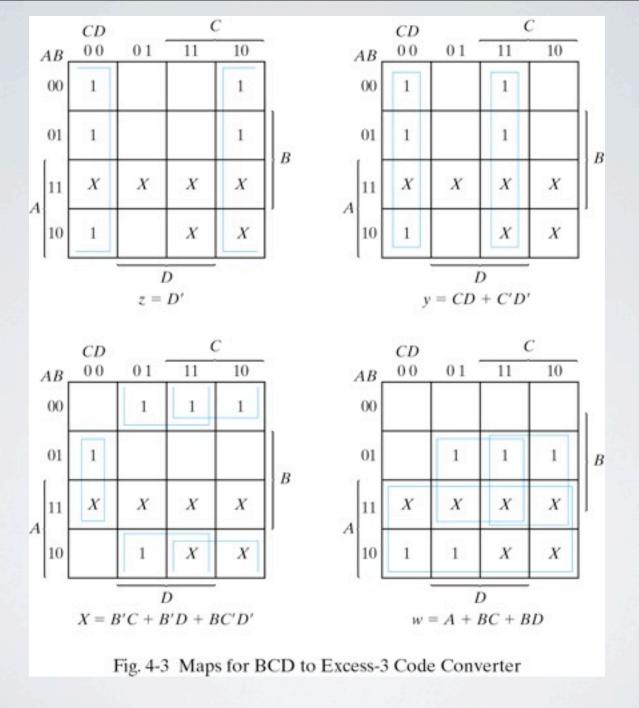

Table 4-2

Truth Table for Code-Conversion Example

| Input BCD |   |    |   | Output Excess-3 Code |     |   |   |

|-----------|---|----|---|----------------------|-----|---|---|

| Α         | В | C  | D | w                    | X   | У | Z |

| 0         | 0 | 0  | 0 | 0                    | 0   | 1 | 1 |

| 0         | 0 | 0  | 1 | 0                    | 1   | 0 | 0 |

| 0         | 0 | 1  | 0 | 0                    | - 1 | 0 | 1 |

| 0         | 0 | 1  | 1 | 0                    | 1   | 1 | 0 |

| 0         | 1 | 0  | 0 | 0                    | 1   | 1 | 1 |

| 0         | 1 | .0 | 1 | 1                    | 0   | 0 | 0 |

| 0         | 1 | 1  | 0 | 1                    | 0   | 0 | 1 |

| 0         | 1 | 1  | 1 | 1                    | 0   | 1 | 0 |

| 1 -       | 0 | 0  | 0 | 1                    | 0   | 1 | 1 |

| 1         | 0 | 0  | 1 | 1                    | 1   | 0 | 0 |

Table 4-2 BCD to Excess-3 Code

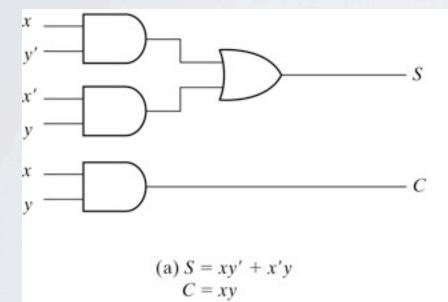

## Table 4-3 Half Adder x y C S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0

Fig. 4-5 Implementation of Half-Adder

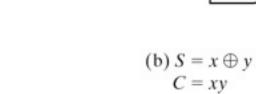

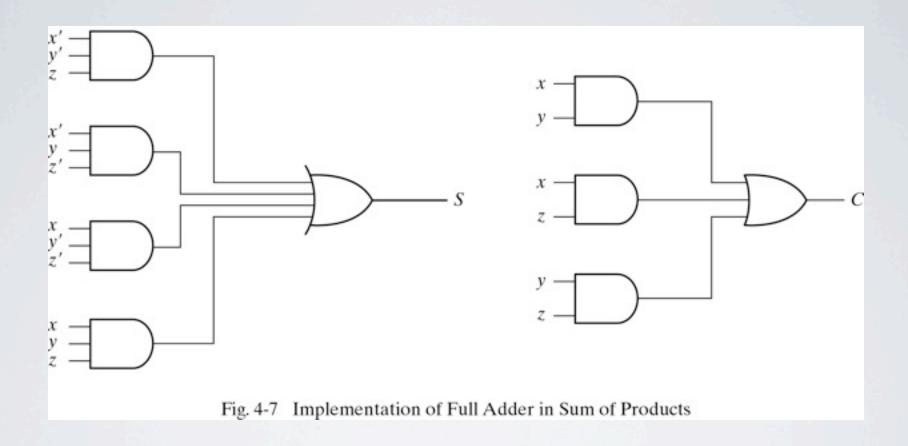

| х | У | Z  | С | S |

|---|---|----|---|---|

| 0 | 0 | 0  | 0 | 0 |

| 0 | 0 | 1  | 0 | 1 |

| 0 | 1 | 0  | 0 | 1 |

| 0 | 1 | 1. | 1 | 0 |

| 1 | 0 | 0  | 0 | 1 |

| 1 | 0 | 1  | 1 | 0 |

| 1 | 1 | 0  | 1 | 0 |

| 1 | 1 | 1  | 1 | 1 |

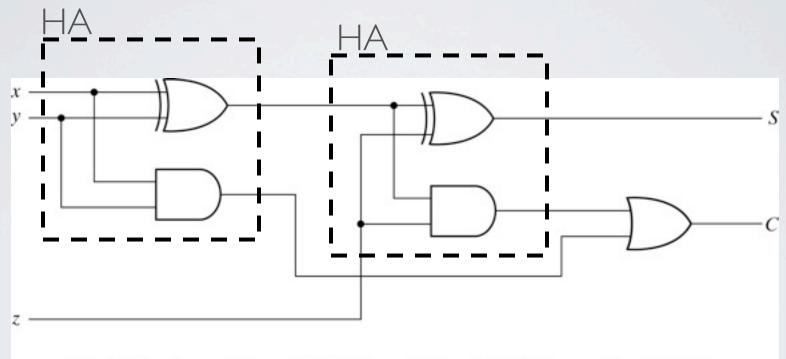

Fig. 4-8 Implementation of Full Adder with Two Half Adders and an OR Gate

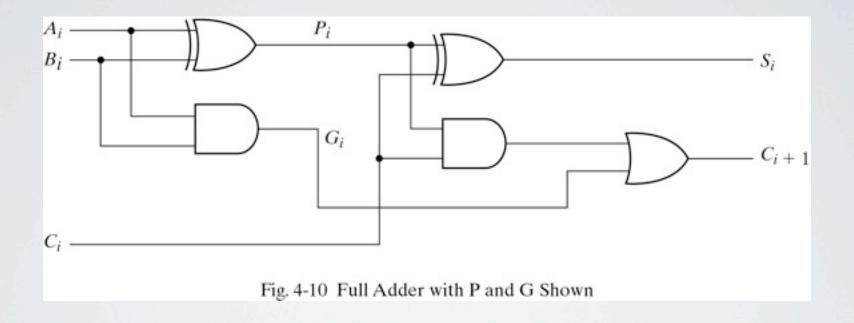

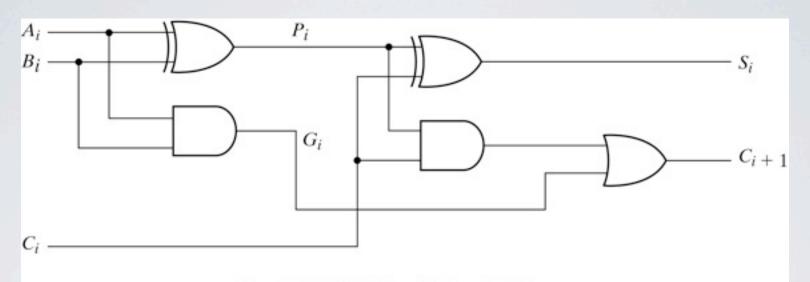

$$P_i = A_i \oplus B_i$$

$$G_i = A_i B_i$$

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i C_i$$

Fig. 4-10 Full Adder with P and G Shown

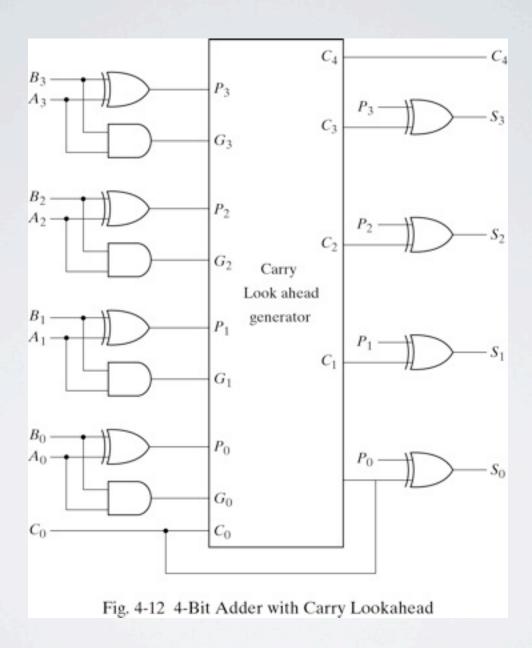

$$P_i = A_i \oplus B_i$$

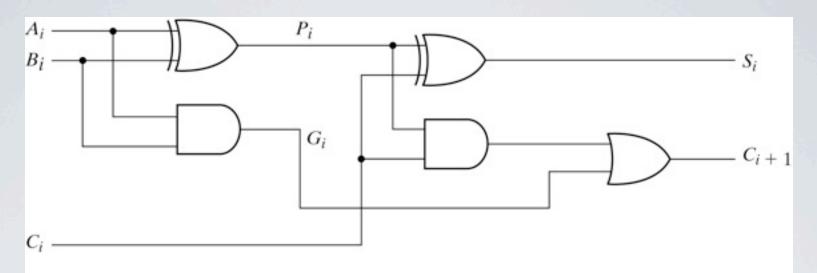

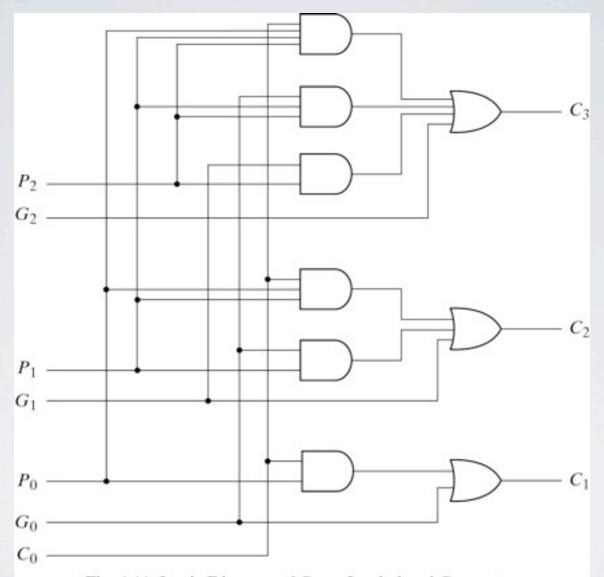

$S_i = P_i \oplus C_i$   $C_{i+1} = G_i + P_i C_i$   $C_0 = \text{input carry}$   $C_1 = G_0 + P_0 C_0$   $C_2 = G_1 + P_1 C_1 = G_1 + P_1 (G_0 + P_0 C_0) = G_1 + P_1 G_0 + P_1 P_0 C_0$   $C_3 = G_2 + P_2 C_2 = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 C_0$

Fig. 4-11 Logic Diagram of Carry Lookahead Generator

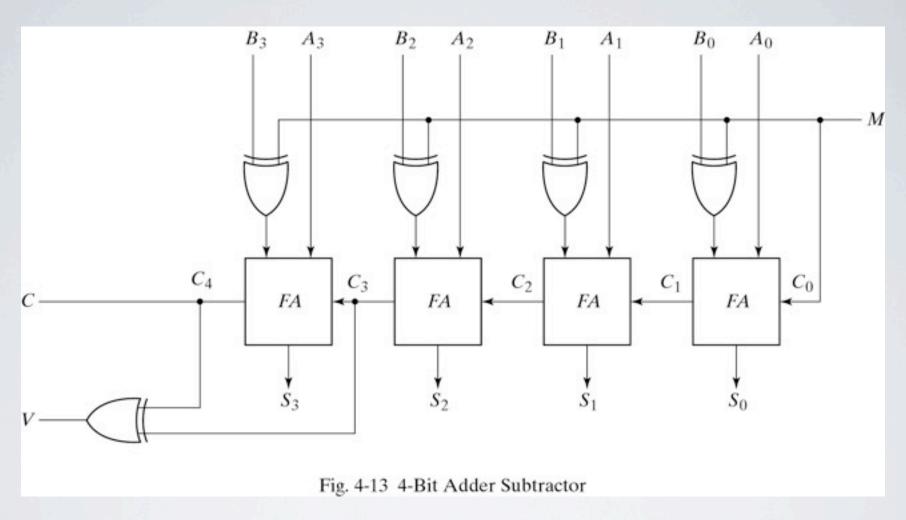

M=1 complements the B-bits and adds 1, thus forming the 2's complement of B

| carries: 0 | 1         | carries: 1 | 0         |

|------------|-----------|------------|-----------|

| +70        | 0 1000110 | -70        | 1 0111010 |

| +80        | 0 1010000 | -80        | 1 0110000 |

| +150       | 1 0010110 | -150       | 0 1101010 |

overflow occurs if:

For unsigned numbers: carry out of msb

for Signed numbers: if carry into sign bit is different than carry out of sign bit

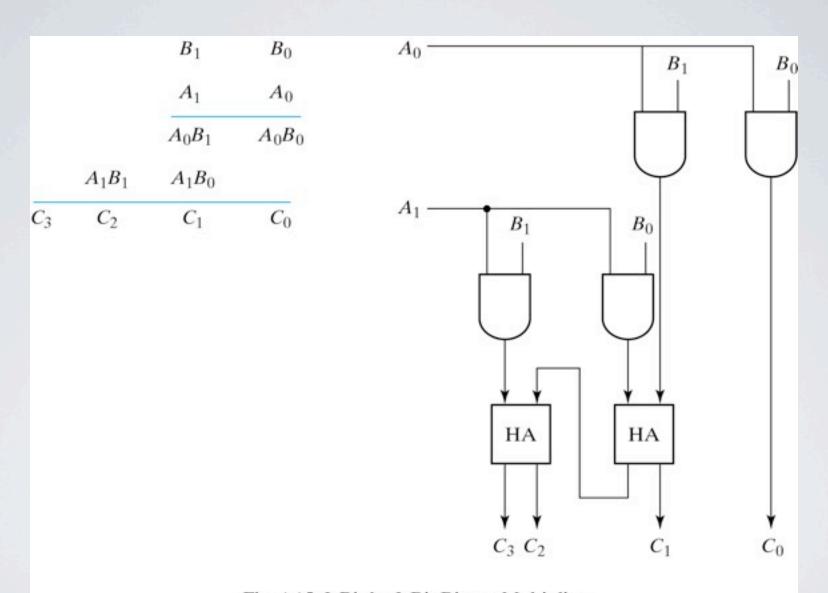

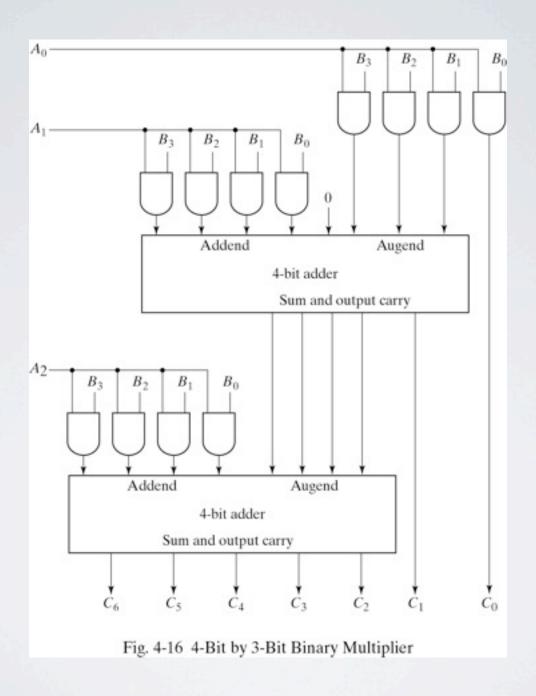

Fig. 4-15 2-Bit by 2-Bit Binary Multiplier

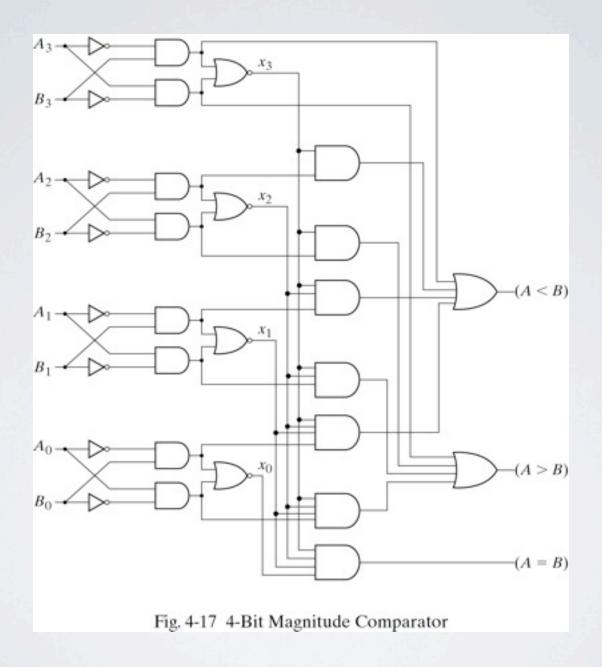

## MAGNITUDE COMPARATOR

$$A = A_3 A_2 A_1 A_0$$

$$B = B_3 B_2 B_1 B_0$$

$$x_i = A_i B_i + A'_i B'_i$$

for  $i = 0, 1, 2, 3$

$(A = B) = x_3 x_2 x_1 x_0$

$$(A > B) = A_3 B_3' + x_3 A_2 B_2' + x_3 x_2 A_1 B_1' + x_3 x_2 x_1 A_0 B_0'$$

$$(A < B) = A_3' B_3 + x_3 A_2' B_2 + x_3 x_2 A_1' B_1 + x_3 x_2 x_1 A_0' B_0$$