## Multiplexers and Decoders

INEL 4205 - Ch. 4 - Spring 2012

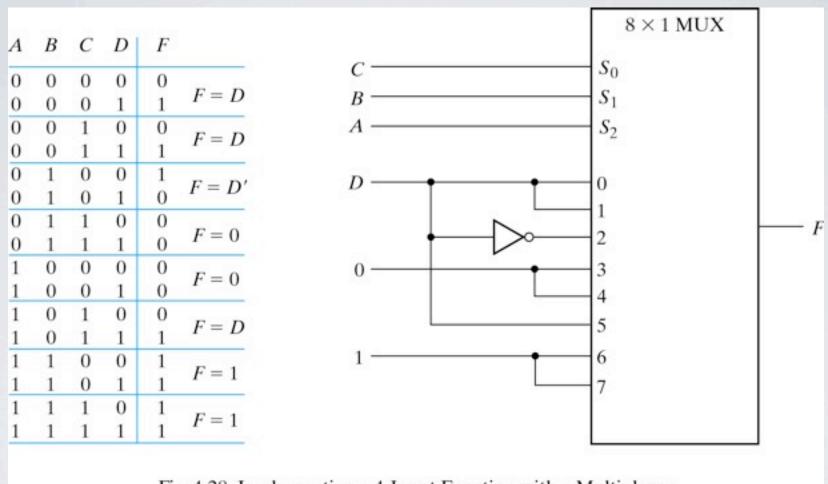

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

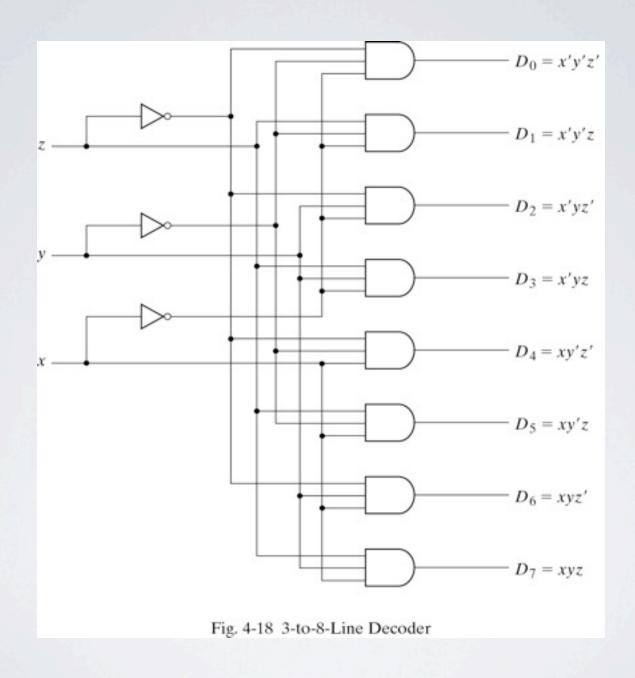

**Table 4-6** *Truth Table of a 3-to-8-Line Decoder*

| Inputs |   |   | Outputs        |       |                |       |       |       |       |       |  |

|--------|---|---|----------------|-------|----------------|-------|-------|-------|-------|-------|--|

| x      | у | Z | D <sub>0</sub> | $D_1$ | D <sub>2</sub> | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ |  |

| 0      | 0 | 0 | 1              | 0     | 0              | 0     | 0     | 0     | 0     | 0     |  |

| 0      | 0 | 1 | 0              | 1     | 0              | 0     | 0     | 0     | 0     | 0     |  |

| 0      | 1 | 0 | 0              | 0     | 1              | 0     | 0     | 0     | 0     | 0     |  |

| 0      | 1 | 1 | 0              | 0     | 0              | 1     | 0     | 0     | 0     | 0     |  |

| 1      | 0 | 0 | 0              | 0     | 0              | 0     | 1     | 0     | 0     | 0     |  |

| 1      | 0 | 1 | 0              | 0     | 0              | 0     | 0     | 1     | 0     | 0     |  |

| 1      | 1 | 0 | 0              | 0     | 0              | 0     | 0     | 0     | 1     | 0     |  |

| 1      | 1 | 1 | 0              | 0     | 0              | 0     | 0     | 0     | 0     | 1     |  |

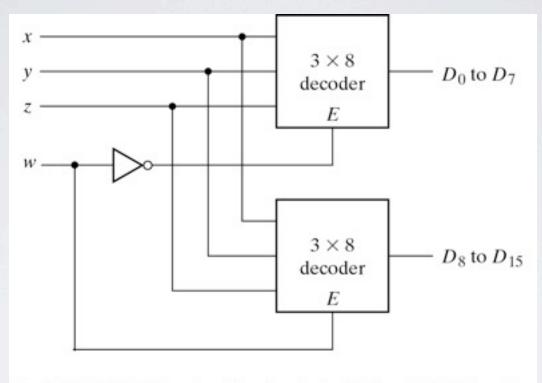

Fig. 4-20  $\,4 \times 16$  Decoder Constructed with Two  $3 \times 8$  Decoders

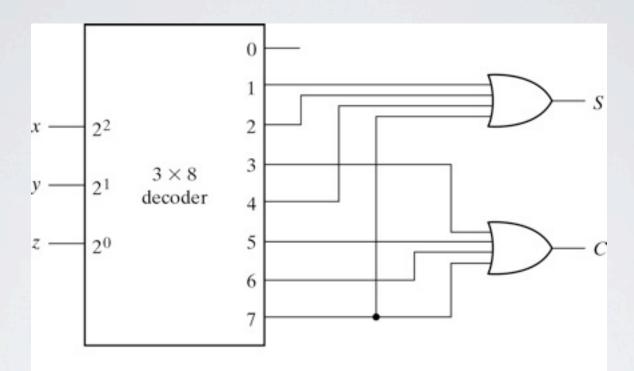

Fig. 4-21 Implementation of a Full Adder with a Decoder

**Table 4-7** *Truth Table of Octal-to-Binary Encoder*

| Inputs |       |       |       |       |       |       |       |      | Outputs |    |   |  |

|--------|-------|-------|-------|-------|-------|-------|-------|------|---------|----|---|--|

| $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | 1 90 | x       | .y | z |  |

| 1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | -    | 0       | 0  | 0 |  |

| 0      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 49   | 0       | 0  | 1 |  |

| 0      | 0     | 1     | 0.3   | 0     | 0     | 0     | 0     |      | 0       | 1  | 0 |  |

| 0      | 0     | 0     | 1     | 0     | 0     | 0     | 0     |      | 0       | 1  | 1 |  |

| 0      | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1/4  | 1       | 0  | 0 |  |

| 0      | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 40   | 1       | 0  | 1 |  |

| 0      | 0     | 0     | 0     | 0     | 0     | 1     | 0     |      | 1       | 1  | 0 |  |

| 0      | 0     | 0     | 0 .   | 0     | 0     | 0     | 1     |      | 1       | 1  | 1 |  |

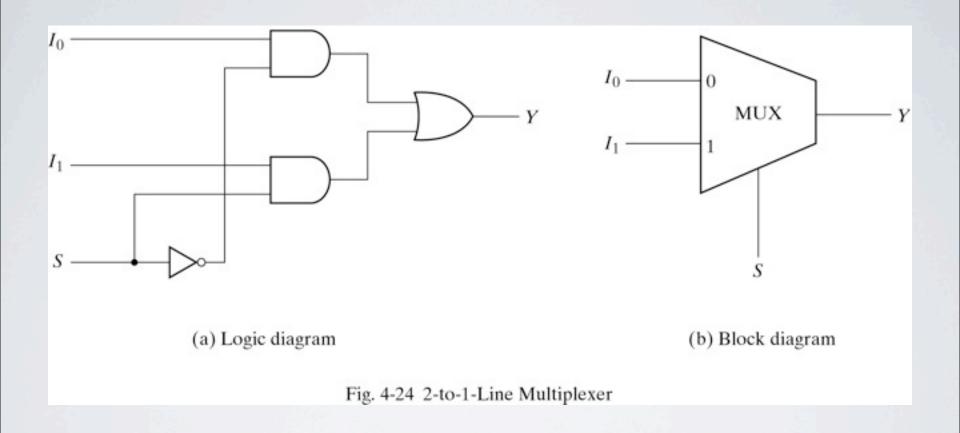

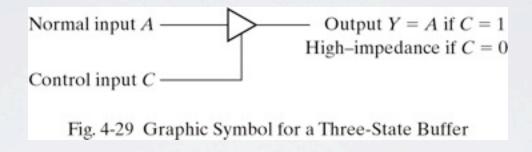

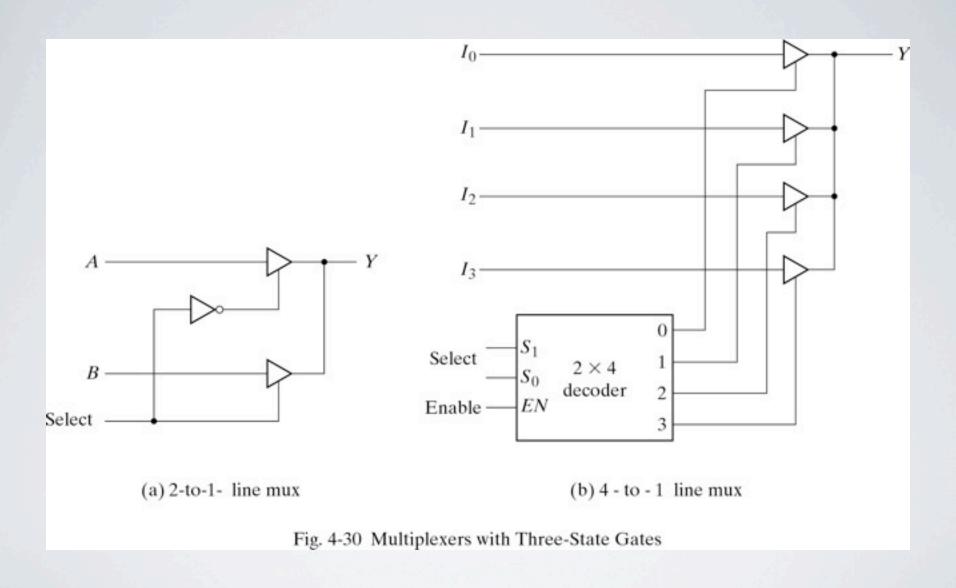

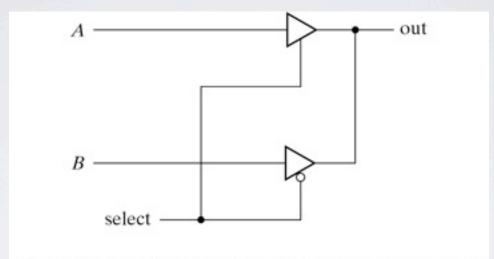

Fig. 4-32 2-to-1-Line Multiplexer with Three-State Buffers