# CHAPTER 5 SEQUENTIAL LOGIC

INEL 4205 LOGIC CIRCUITS

SPRING 2008

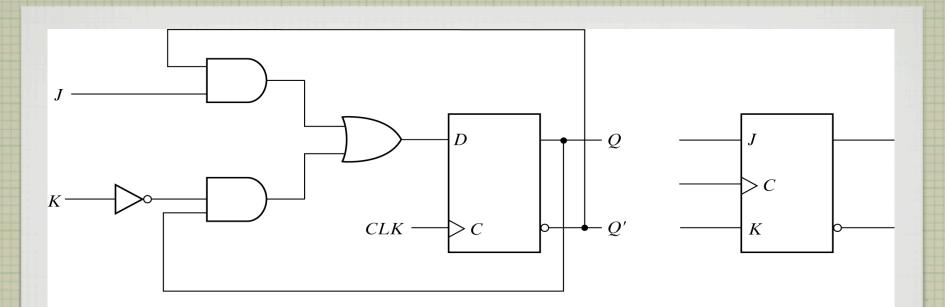

(a) Circuit diagram

(b) Graphic symbol

| JK | Flip- | Flop      | ant of the clock. |

|----|-------|-----------|-------------------|

| J  | K     | Q(t+1)    | )                 |

| 0  | 0     | Q(t)      | No change         |

| 0  | 1     | 0         | Reset             |

| 1  | 0     | E 10 enos | Set               |

| 1  | 1     | Q'(t)     | Complement        |

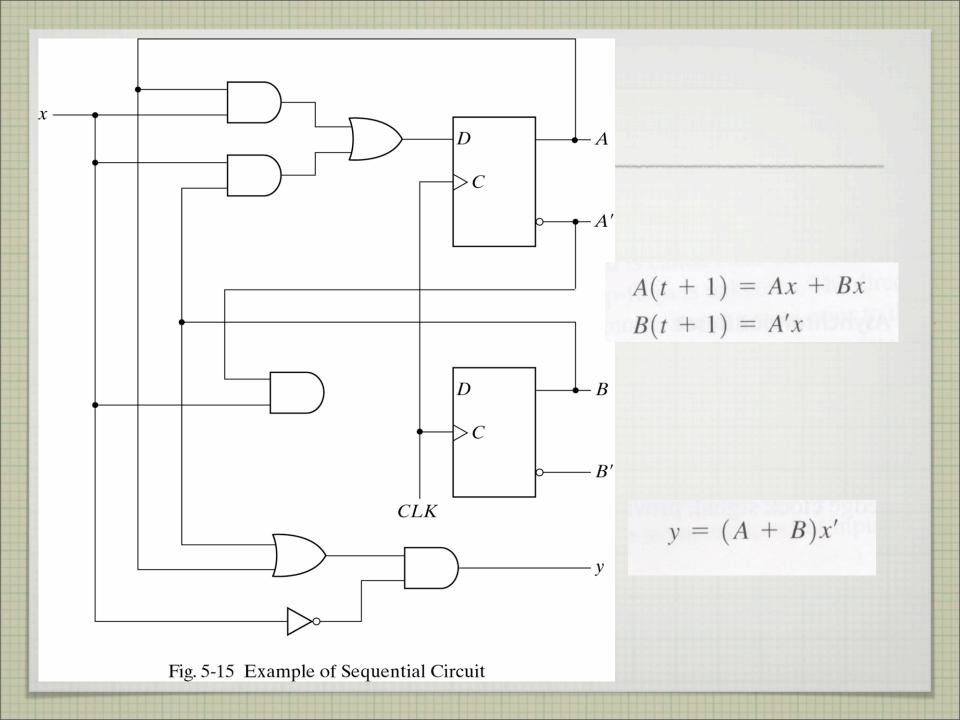

$$A(t + 1) = Ax + Bx$$

$$B(t + 1) = A'x$$

#### STATE EQUATIONS OR

#### TRANSITION EQUATIONS

$$y = (A + B)x'$$

#### OUTPUT BOOLEAN EQUATION

Table 5-2State Table for the Circuit of Fig. 5-15

| Present<br>State |   | Input | Next<br>State |   | Output |

|------------------|---|-------|---------------|---|--------|

| A                | В | x     | A             | В | y      |

| 0                | 0 | 0     | 0             | 0 | 0      |

| 0                | 0 | 1     | 0             | 1 | 0      |

| 0                | 1 | 0     | 0             | 0 | 1      |

| 0                | 1 | 1     | 1             | 1 | 0      |

| 1                | 0 | 0     | 0             | 0 | 1      |

| 1                | 0 | 1     | 1             | 0 | 0      |

| 1                | 1 | 0     | 0             | 0 | 1      |

| 1                | 1 | 1     | 1             | 0 | 0      |

Table 5-3

Second Form of the State Table

| Present<br>State | Next S       | tate         | Output              |              |  |

|------------------|--------------|--------------|---------------------|--------------|--|

|                  | x = <b>0</b> | <i>x</i> = 1 | <i>x</i> = <b>0</b> | <i>x</i> = 1 |  |

| AB               | AB           | AB           | у                   | у            |  |

| 00               | 00           | 01           | 0                   | 0            |  |

| 01               | 00           | 11           | 1 Inter             | 0            |  |

| 10               | 00           | 10           | 1                   | 0            |  |

| 11               | . 00         | 10           | 1                   | 0            |  |

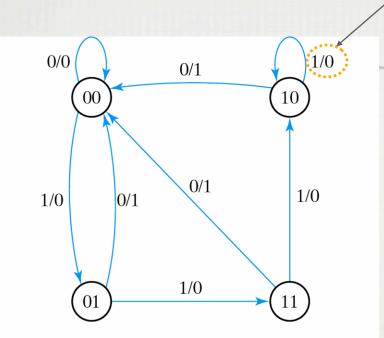

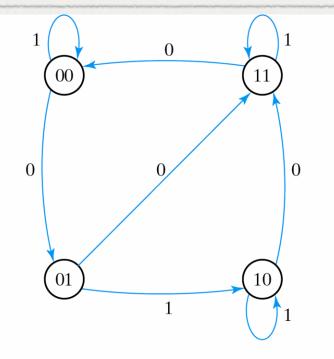

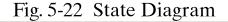

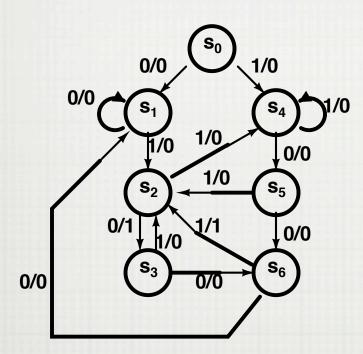

Fig. 5-16 State Diagram of the Circuit of Fig. 5-15

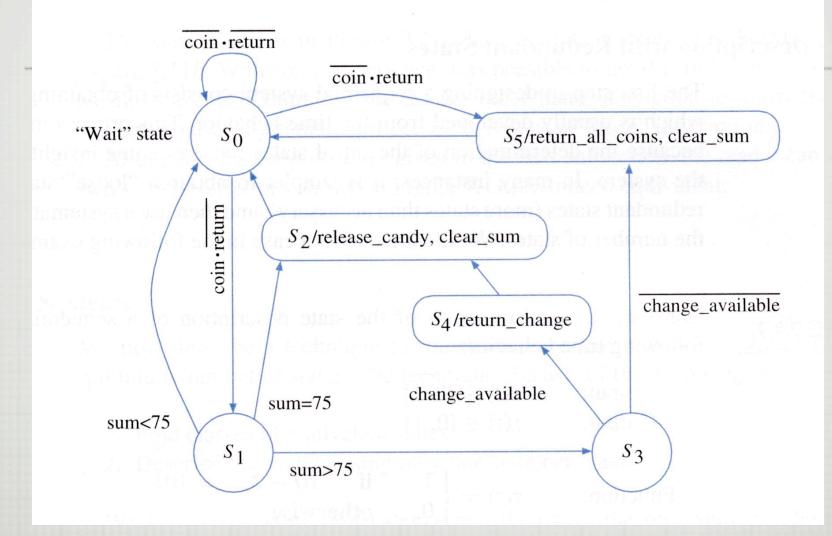

### MEALY FINITE STATE MACHINE (FSM) - OUTPUT IS A FUNCTION OF PRESENT STATE AND INPUT

/O REPRESENTS THE OUTPUT / DURING THE PRESENT STATE WITH THE GIVEN INPUT

2. DRAW THE STATE DIAGRAM

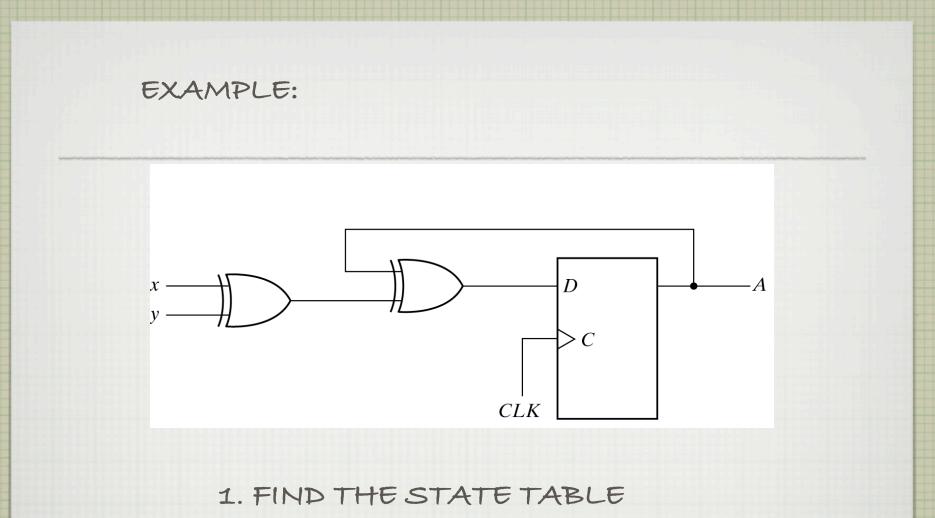

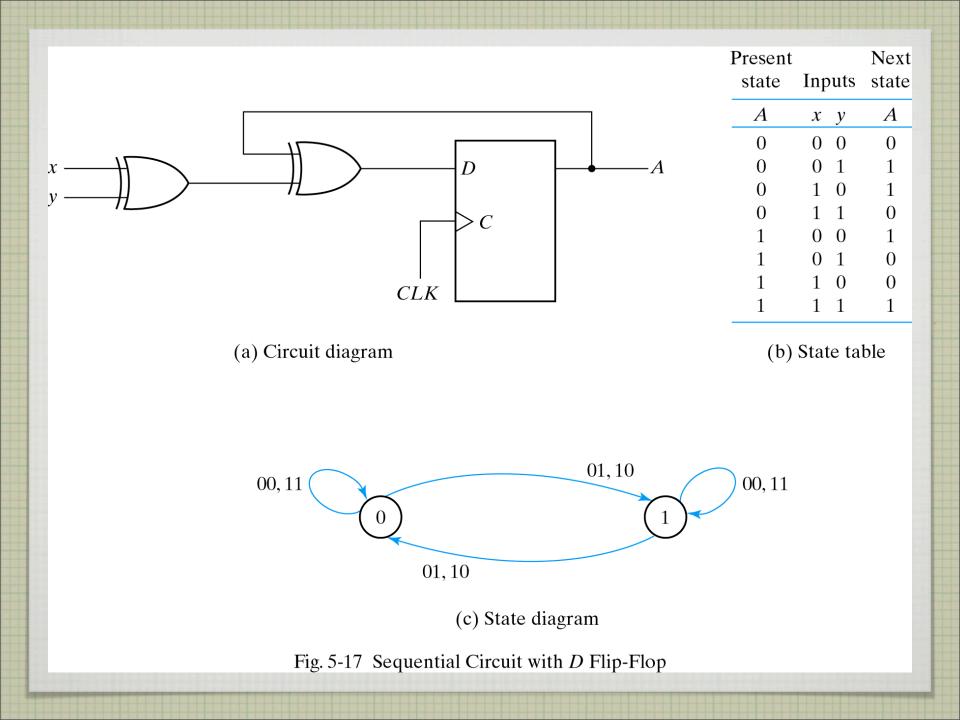

**5-6** A sequential circuit with two *D* flip-flops, *A* and *B*; two inputs, *x* and *y*; and one output, *z*, is specified by the following next-state and output equations:

$$A(t + 1) = x'y + xA$$

$$B(t + 1) = x'B + xA$$

$$z = B$$

(a) Draw the logic diagram of the circuit.(b) List the state table for the sequential circuit.(c) Draw the corresponding state diagram.

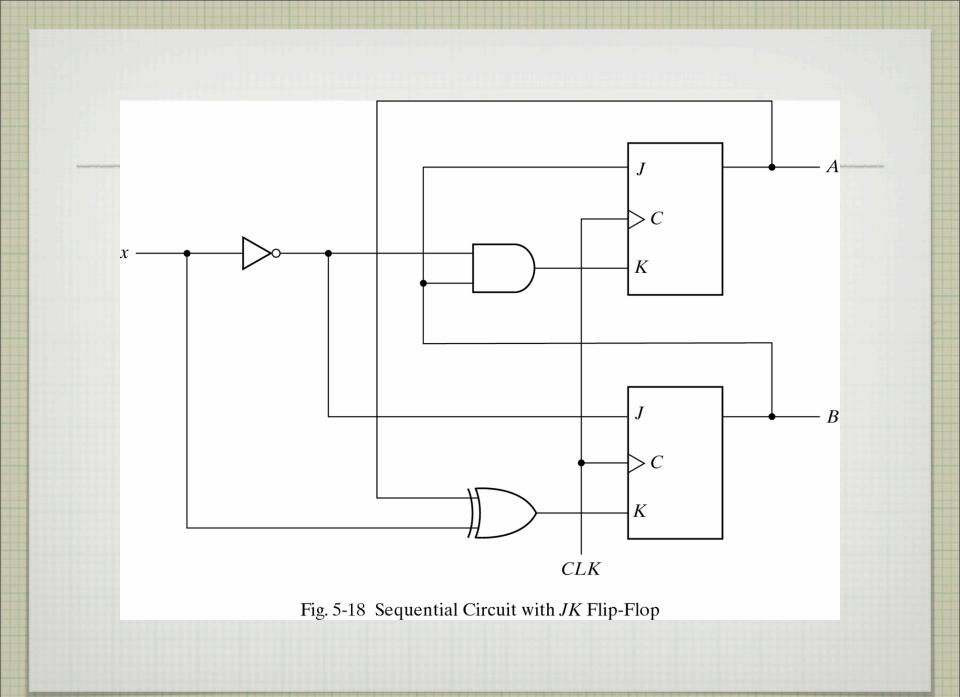

flip-flop input equations

$$J_A = B K_A = Bx'$$

$$J_B = x' K_B = A'x + Ax' = A \oplus x$$

#### Table 5-4

### State Table for Sequential Circuit with JK Flip-Flops

|   | esent<br>ate | Input |     | ext<br>ate | Flip-Flop<br>Inputs |                | Flip-Flop<br>Inputs |                |

|---|--------------|-------|-----|------------|---------------------|----------------|---------------------|----------------|

| A | В            | x     | A   | В          | J <sub>A</sub>      | K <sub>A</sub> | J <sub>B</sub>      | K <sub>B</sub> |

| 0 | 0            | 0     | 0   | 1          | 0                   | 0              | 1                   | 0              |

| 0 | 0            | 1     | 0   | 0          | 0                   | 0              | 0                   | 1              |

| 0 | 1            | 0     | 1   | 1          | 1                   | 1              | 1                   | 0              |

| 0 | 1            | 1     | • 1 | 0          | 1                   | 0              | 0                   | 1              |

| 1 | 0            | 0     | 1   | 1          | 0                   | 0              | 1                   | 1              |

| 1 | 0            | 1     | 1   | 0          | 0                   | 0              | 0                   | 0              |

| 1 | 1            | 0     | 0   | 0          | 1                   | 1              | 1                   | 1              |

| 1 | 1            | 1     | 1   | 1          | 1                   | 0              | 0                   | 0              |

Fig. 5-19 State Diagram of the Circuit of Fig. 5-18

**5-10** A sequential circuit has two JK flip-flops A and B, two inputs x and y, and one output z. The flip-flop input equations and circuit output equation are

$$J_A = Bx + B'y' \qquad K_A = B'xy'$$

$$J_B = A'x \qquad K_B = A + xy$$

$$z = Ax'y' + Bx'y'$$

(a) Draw the logic diagram of the circuit. (b) Tabulate the state table.

(c) Derive the state equations for A and B.

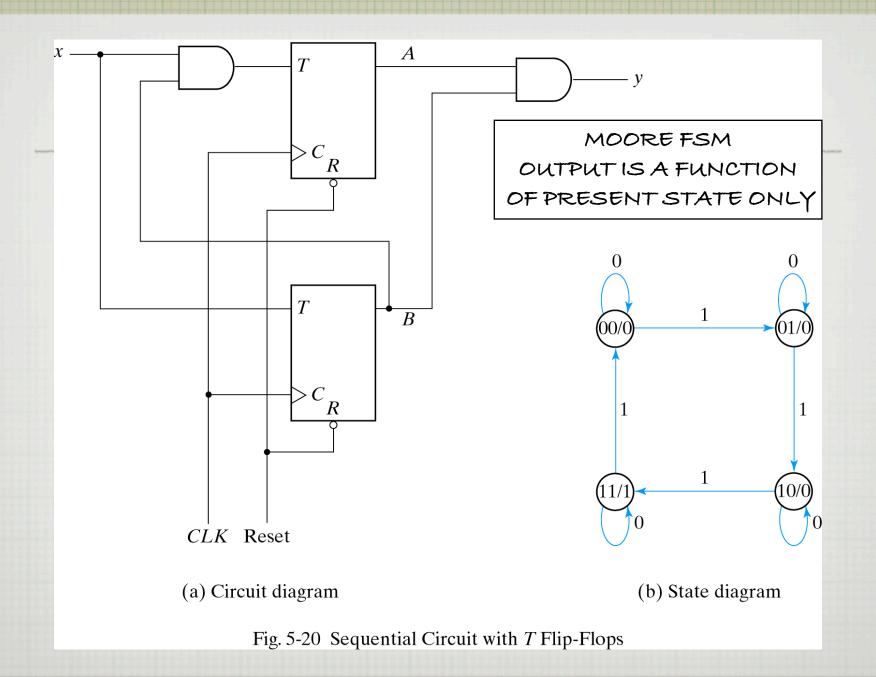

#### DESIGN PROCEDURE

- **1.** From the word description and specifications of the desired operation, derive a state diagram for the circuit.

- 2. Reduce the number of states if necessary.

- **3.** Assign binary values to the states.

- 4. Obtain the binary-coded state table.

- 5. Choose the type of flip-flops to be used.

- 6. Derive the simplified flip-flop input equations and output equations.

- 7. Draw the logic diagram.

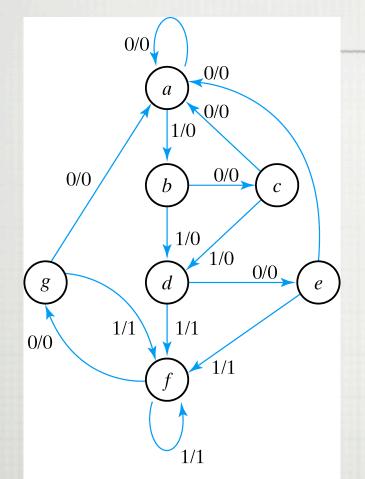

#### STATE REDUCTION

| Table | 5-6   |

|-------|-------|

| State | Table |

|               | Next State   |   | Output       |              |  |

|---------------|--------------|---|--------------|--------------|--|

| Present State | x = <b>0</b> |   | x = <b>0</b> | <i>x</i> = 1 |  |

| a             | а            | Ь | 0            | 0            |  |

| b             | С            | d | 0            | 0            |  |

| С             | а            | d | 0            | 0            |  |

| d             | е            | f | 0            | 1            |  |

| е             | а            | f | 0            | 1            |  |

| f             | g            | f | 0            | 1            |  |

| g             | а            | f | 0            | 1            |  |

STATES ARE APPLICATION-DEPENDANT. THE NAMES GIVEN HERE (A, B, C, D, ...) ARE ARBITRARY. IT IS ASSUMED THAT ONLY THE OUTPUT RESPONSE TO A GIVEN SEQUENCE OF INPUTS IS IMPORTANT.

|               | Next State   |              | Output       |              |  |

|---------------|--------------|--------------|--------------|--------------|--|

| Present State | x = <b>0</b> | <i>x</i> = 1 | x = <b>0</b> | <i>x</i> = 1 |  |

| a             | а            | Ь            | 0            | 0            |  |

| Ь             | С            | d            | 0            | 0            |  |

| С             | а            | d            | 0            | 0            |  |

| d             | е            | f            | 0            | 1            |  |

| е             | а            | f            | 0            | 1            |  |

| f             | g            | f            | 0            | 1            |  |

| g             | а            | f            | 0            | 1            |  |

Table 5-6

An algorithm for the state reduction of a completely specified state table is given here without proof: "Two states are said to be equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state or to an equivalent state." When two states are equivalent, one of them can be removed without altering the input–output relationships.

### Table 5-6State Table

|               | Next         | State        | Output       |   |  |

|---------------|--------------|--------------|--------------|---|--|

| Present State | x = <b>0</b> | <i>x</i> = 1 | x = <b>0</b> |   |  |

| a             | а            | Ь            | 0            | 0 |  |

| b             | С            | d            | 0            | 0 |  |

| С             | а            | d            | 0            | 0 |  |

| d             | е            | f            | 0            | 1 |  |

| е             | а            | f            | 0            | 1 |  |

| f             | g            | f            | 0            | 1 |  |

| g             | a            | f            | 0            | 1 |  |

## Table 5-7Reducing the State Table

|               | Next         | State        | Output       |              |  |

|---------------|--------------|--------------|--------------|--------------|--|

| Present State | x = <b>0</b> | <i>x</i> = 1 | x = <b>0</b> | <i>x</i> = 1 |  |

| а             | а            | Ь            | 0            | 0            |  |

| Ь             | С            | d            | 0            | 0            |  |

| С             | · a          | d            | 0            | 0            |  |

| d             | е            | f            | 0            | 1            |  |

| е             | а            | f            | 0            | 1            |  |

| f             | е            | f            | 0            | 1            |  |

| Fable 5-8       Reduced State Table |              |              |              |              |  |  |  |

|-------------------------------------|--------------|--------------|--------------|--------------|--|--|--|

| deced to former star                | Next         | State        | Output       |              |  |  |  |

| Present State                       | x = <b>0</b> | <i>x</i> = 1 | x = <b>0</b> | <i>x</i> = 1 |  |  |  |

| а                                   | а            | Ь            | 0            | 0            |  |  |  |

| Ь                                   | С            | d            | 0            | 0            |  |  |  |

| С                                   | а            | d            | 0            | 0            |  |  |  |

| d                                   | е            | d            | 0            | 1            |  |  |  |

| е                                   | а            | d            | 0            | 1            |  |  |  |

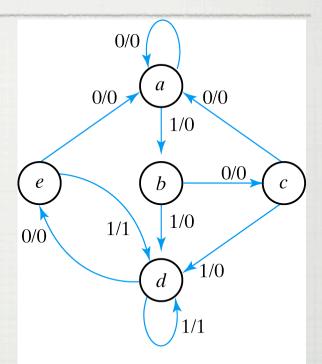

Fig. 5-23 Reduced State Diagram

## **State Assignment**

Table 5-9Three Possible Binary State Assignments

| State | Assignment 1<br>Binary | Assignment 2<br>Gray code | Assignment 3<br>One-hot |

|-------|------------------------|---------------------------|-------------------------|

| а     | 000                    | 000                       | 00001                   |

| b     | 001                    | 001                       | 00010                   |

| С     | 010                    | 011                       | 00100                   |

| d     | 011                    | 010                       | 01000                   |

| е     | 100                    | 110                       | 10000                   |

Table 5-10

Reduced State Table with Binary Assignment 1

|               | Next State   |                     |   | Output              |       |  |

|---------------|--------------|---------------------|---|---------------------|-------|--|

| Present State | x = <b>0</b> | <i>x</i> = <b>1</b> | 6 | <i>x</i> = <b>0</b> | x = 1 |  |

| 000           | 000          | 001                 |   | 0                   | 0     |  |

| 001           | 010          | 011                 |   | 0                   | 0     |  |

| 010           | 000          | 011                 |   | 0                   | 0     |  |

| 011           | 100          | 011                 |   | 0                   | 1     |  |

| 100           | 000          | 011                 |   | 0                   | 1     |  |

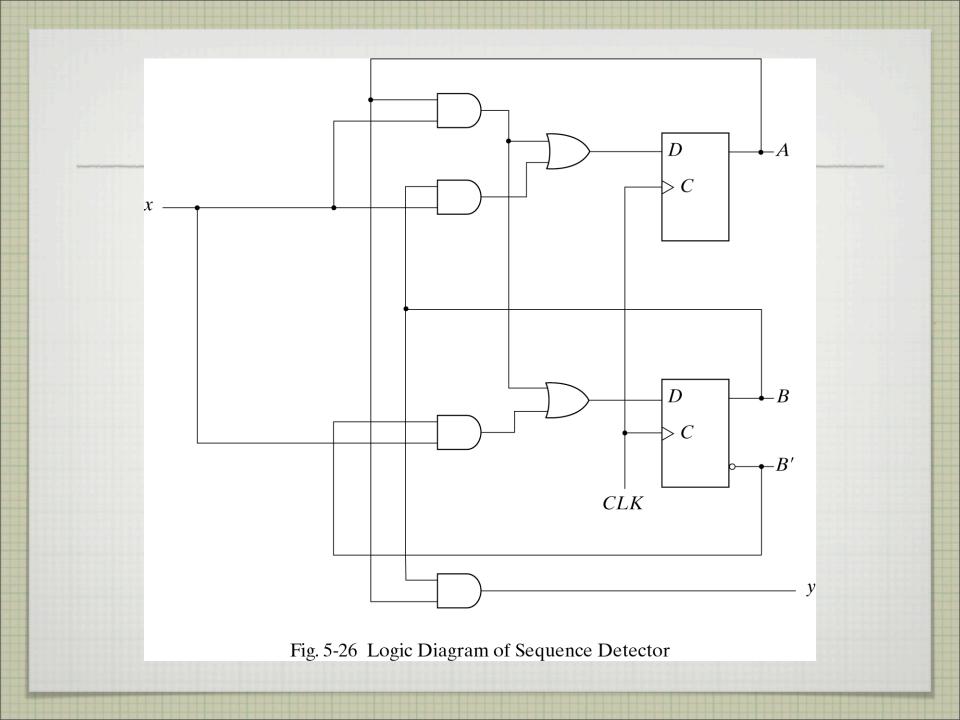

SEQUENCE DETECTOR: CIRCUIT THAT DETECTS 3 CONSECUTIVE 1'S IN A STRING OF BITS COMING THROUGH THE INPUT LINE

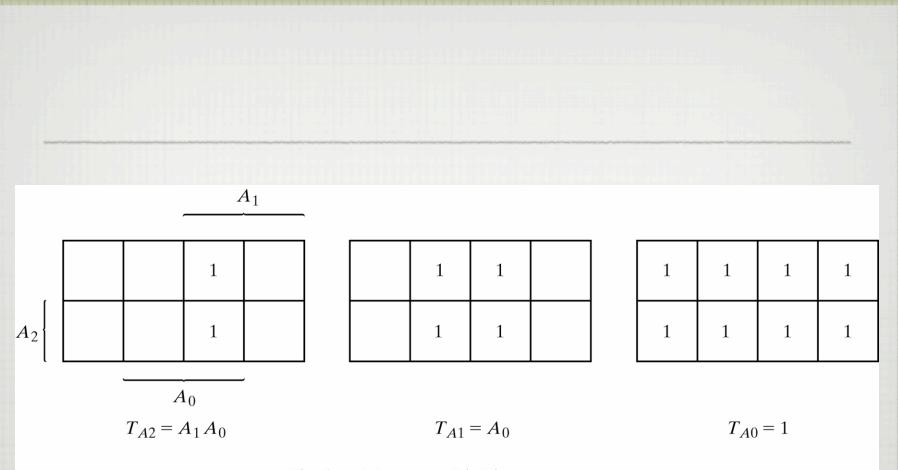

Fig. 5-24 State Diagram for Sequence Detector

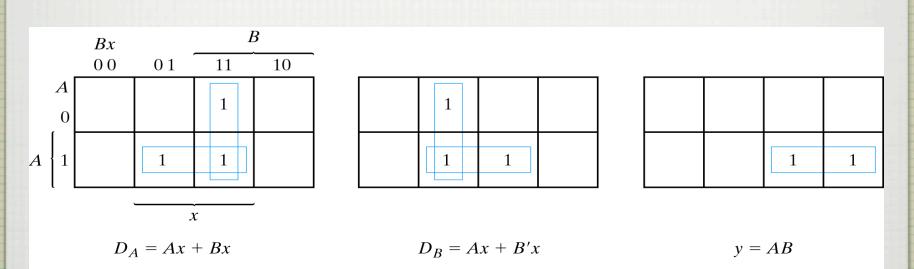

Fig. 5-25 Maps for Sequence Detector

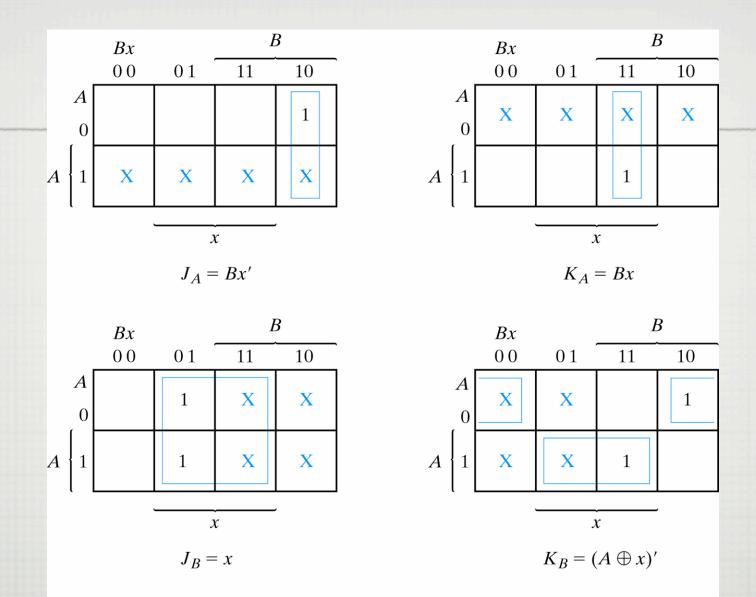

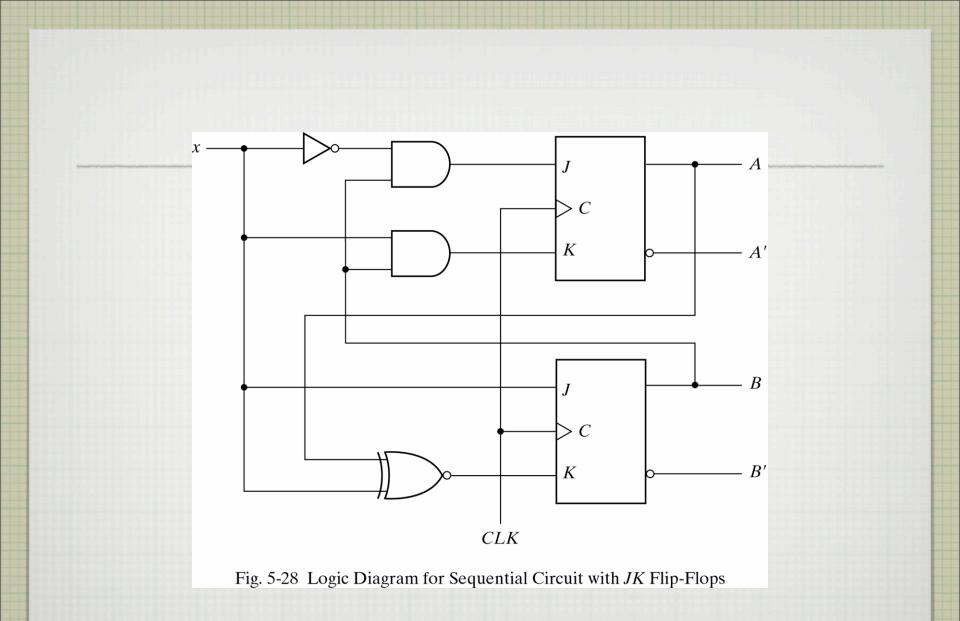

### USING KORTFLIP-FLOPS

## Table 5-12Flip-Flop Excitation Tables

| Q(t)                    | Q(t + 1)      | J | К | Q(t)         | Q(t + 1) | Τ |  |

|-------------------------|---------------|---|---|--------------|----------|---|--|

| 0                       | 0             | 0 | Х | 0            | 0        | 0 |  |

| 0                       | 1 8           | 1 | Х | 0            | 1        | 1 |  |

| 1                       | 0             | X | 1 | 1            | 0        | 1 |  |

| 1                       | 1             | X | 0 | 1            | 1        | 0 |  |

| *********************** | (a) <i>JK</i> |   |   | (b) <i>T</i> |          |   |  |

## Table 5-13State Table and JK Flip-Flop Inputs

| Present<br>State |   | Input    | Next<br>State |    | Fli | Flip-Flop Inputs |                |                |  |

|------------------|---|----------|---------------|----|-----|------------------|----------------|----------------|--|

| Α                | В | <b>x</b> | A             | В  | JA  | K <sub>A</sub>   | J <sub>B</sub> | K <sub>B</sub> |  |

| 0                | 0 | 0        | 0             | 0  | 0   | Х                | 0              | Х              |  |

| 0                | 0 | 1        | 0             | 1  | 0   | Х                | 1              | Χ              |  |

| 0                | 1 | 0        | 1             | 0  | 1   | Χ                | X              | 1              |  |

| 0                | 1 | 1        | 0             | -1 | 0   | Х                | X              | 0              |  |

| 1                | 0 | 0        | 1             | 0  | Х   | 0                | 0              | Χ              |  |

| 1                | 0 | 1        | 1             | 1  | Х   | 0                | 1              | Χ              |  |

| 1                | 1 | 0        | 1             | 1  | Х   | 0                | X              | 0              |  |

| 1                | 1 | 1        | 0             | 0  | Х   | 1                | X              | 1              |  |

mented and goes from the destate to the 4-state as required. Therefore th

Fig. 5-27 Maps for J and K Input Equations

# STATE ASSIGNMENT GUIDELINES

ASSIGN NEIGHBORING CODES IF STATES HAVE THE SAME

NEXT STATE (G1)

PREVIOUS STATE (G2)

OUTPUTS (G3)

PRIORITIZE STATE COMBINATIONS FOR WHICH G1, G2, G3 APPLY MORE THAN ONCE

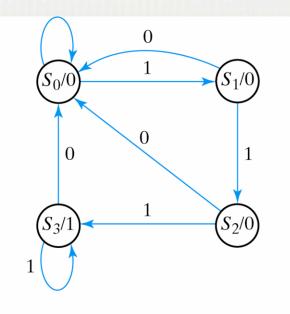

#### **SEQUENCE DETECTOR FOR 010 OR 1001**

| present    |            | xt<br>xl   | out<br>x=0 | put<br>x=l |

|------------|------------|------------|------------|------------|

| S0         | SI         | <b>S</b> 4 | 0          | 0          |

| SI         | SI         | <b>S</b> 2 | 0          | 0          |

| S2         | <b>S</b> 3 | <b>S</b> 4 | Ι          | 0          |

| \$3        | <b>S</b> 6 | <b>S</b> 2 | 0          | 0          |

| S4         | <b>S</b> 5 | <b>S</b> 4 | 0          | 0          |

| <b>S</b> 5 | <b>S</b> 6 | <b>S</b> 2 | 0          | 0          |

| S6         | SI         | <b>S</b> 2 | 0          | Ι          |

S3 5 S5 ARE EQUIVALENT

### **SEQUENCE DETECTOR FOR 010 OR 1001 (CONT)**

| present        |            | xt<br>xl   | out<br>x=0 | • |

|----------------|------------|------------|------------|---|

| S <sub>0</sub> | SI         | <b>S</b> 4 | 0          | 0 |

| SI             | SI         | <b>S</b> 2 | 0          | 0 |

| <b>S</b> 2     | <b>S</b> 3 | <b>S</b> 4 | I          | 0 |

| <b>S</b> 3     | <b>S</b> 6 | <b>S</b> 2 | 0          | 0 |

| S4             | <b>S</b> 3 | <b>S</b> 4 | 0          | 0 |

| S6             | SI         | <b>S</b> 2 | 0          | I |

(S0,S1,S6), (S2, S4), (\$0,\$2,\$4), (\$1,\$3,\$6) G1

□ (S1,S2), (S3,S4) G2 × 2

(S0, S1, S3, S4) G3

|   | 00 | 01 | П  | 10 |

|---|----|----|----|----|

| 0 | sO | sl | s6 | Х  |

| Ι | s4 | s2 | X  | s3 |

ONE POSSIBILITY

### **SEQUENCE DETECTOR FOR 010 OR 1001 (CONT)**

| present |     | Next |     | output |     |

|---------|-----|------|-----|--------|-----|

|         |     | x=0  | x=I | x=0    | x=I |

| s0      | 000 | 001  | 100 | 0      | 0   |

| sl      | 001 | 001  | 101 | 0      | 0   |

| s2      | 101 | 110  | 100 | Ι      | 0   |

| s3      | 110 | 011  | 101 | 0      | 0   |

| s4      | 100 | 110  | 100 | 0      | 0   |

| s6      | 011 | 001  | 101 | 0      | I   |

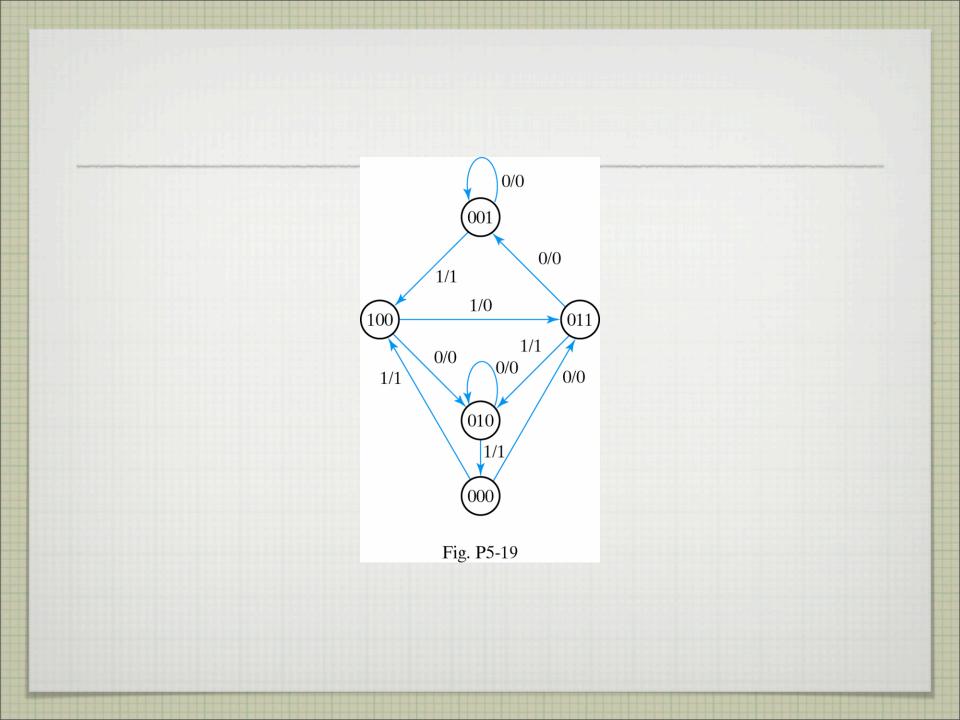

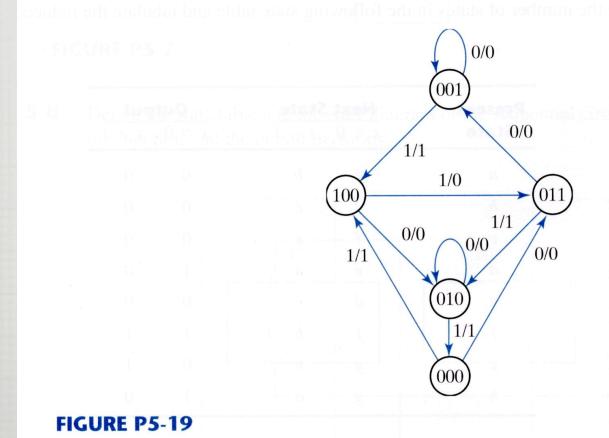

- **5-19** A sequential circuit has three flip-flops A, B, C; one input x; and one output y. The state diagram is shown in Fig. P5-19. The circuit is to be designed by treating the unused states as don't-care conditions. Analyze the circuit obtained from the design to determine the effect of the unused states.

- (a) Use *D* flip-flops in the design.

(b) Use *JK* flip-flops in the design.

AB 00 01 11 D 01 AB 10 11 5-19 (2) 00 Input state output Present 01 01 state ABC 11 X ABC x 8 × X X X 11 000 0 10 0 011 X 10 X  $\mathcal{D}B = A + \mathcal{C}' x' + B \mathcal{C} x$ 100 Ò DA=A'B'x 001 001 O 100 001 010 010 0 0 000 1 010 001 0 0 011 × × 010 × × 1 011 0 010 X × 0 00 011 0 y = A' x100 DC = Cx' + Ax + A'B'x' $d(\mathbf{A}, \mathbf{B}, \mathbf{C}, \mathbf{x}) = \mathcal{E}(10, 11, 12, 13, 14, 15)$

self - correcting 110 0/0 on (b) Use JK flip flips: (b) same state lable as in part(a). Flip-flop inputs KA=1 JA=Bx JA KA JB KBIJC KC KB=c'x+Cx' KC=x XXXXO XXO-JB = Atc'x' 0 \*\*\*\*\*\*\* -000 × ×××--0××00××0 JC = Ax+ABx 0-0000XX y=A'x XXOI Self-corecting because KA=1 ××

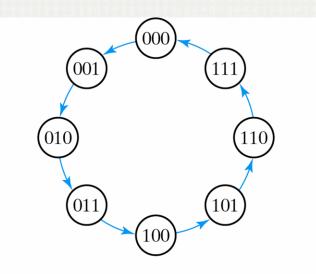

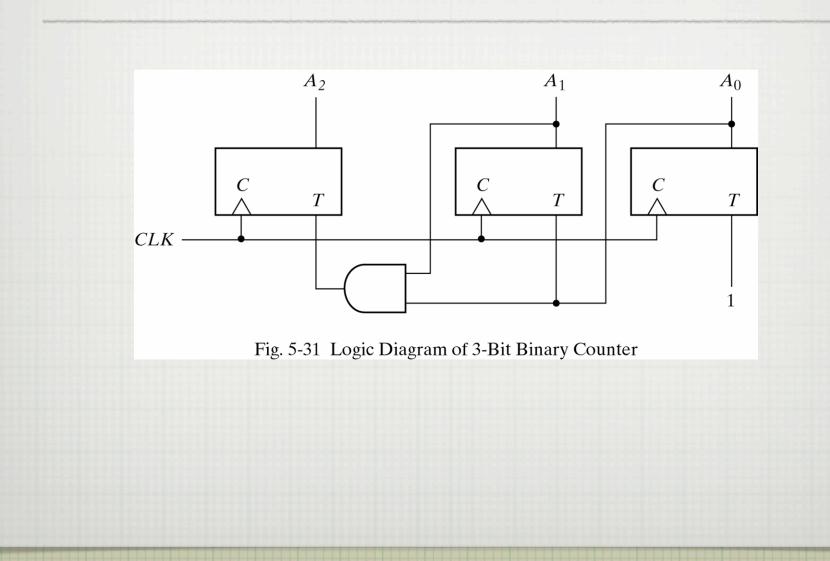

Fig. 5-29 State Diagram of 3-Bit Binary Counter

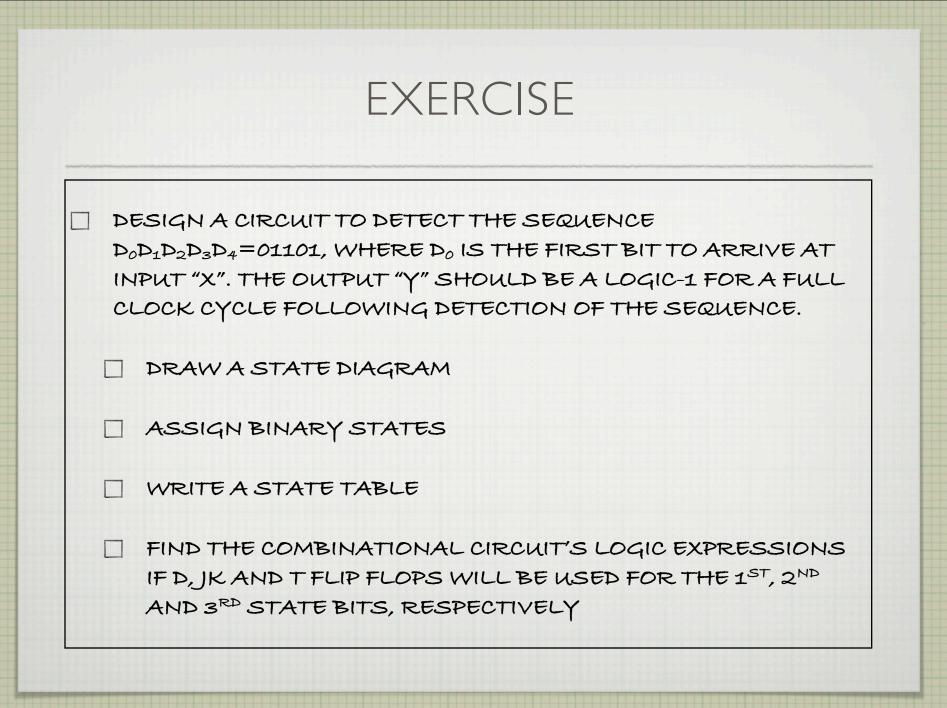

## EXERCISE

DRAW THE STATE DIAGRAM FOR A CIRCUIT THAT DETECTS THE SEQUENCE "0101" (LEFT-TO-RIGHT) USING

A MOORE FINITE STATE MACHINE (FSM)

A MEALY FSM

## EXERCISE

FOR A CLOCKED SYNCHRONOUS STATE MACHINE WITH TWO INPUTS, X AND Y, AND ONE OUTPUT, Z, THE OUTPUT SHOULD BE 1 IF THE NUMBER OF 1 INPUTS ON X AND Y SINCE RESET IS A MULTIPLE OF 4, AND 0 OTHERWISE. DRAW THE STATE DIAGRAM FOR A

MOORE MACHINE

MEALY MACHINE