# **Chapter 4**

# **Operational Amplifiers**

# 4.1 Introduction

The operational amplifier (*opamp* for short) is perhaps the most important building block for the design of analog circuits. Combined with simple negative feedback networks, opamps allow engineers to build many circuits in a simple fashion, at low cost and using relatively few discrete components. Good knowledge of the opamp characteristics and aplications is essencial for a sucessful analog engineer.

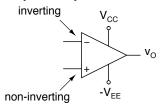

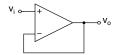

Opamps are *differential amplifiers*, and their output voltage is proportional to the difference of the two input voltages. The opamp's schematic symbol is shown below. The two input terminals, called the inverting and non-inverting, are labeled with - and +, respectively. Most opamps require two supplies that are most often connected to positive and negative voltages of equal magnitute. The supply connections may or may not be shown in a schematic diagram.

An ideal opamp has infinite gain and input impedance, and its input terminals take no input current. Negative feedback causes the voltage between inverting and non-inverting inputs to vanish. It is said that they are *virtually* connected. When one of the two inputs is connected to ground, the other one is said to be a *virtual ground*.

# 4.2 Basic Opamp Circuits

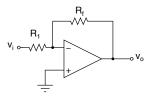

#### 1. Inverting amplifier

Since the opamp takes no input current, the same current flows through  $R_1$  and  $R_2$ . Because the non-inverting input is grounded, a *virtual ground* exist in the inverting input by virtue of the infinite gain and the negative feedback being used. Thus  $v_i = i \times R_1$  and  $v_o = -i \times R_2$ . It follows that the gain of the inverting amplifier is  $\frac{v_o}{v_i} = -\frac{R_2}{R_1}$ .

The input impedance  $R_i = R_1$ . To find the output impedance, apply a test current source to the output and ground to  $v_i$ . Because of virtual ground, no current flows through  $R_1$ . Since no current flows into the inverting input, the current through  $R_2$  must be 0 as well. Thus, independently of the test current,  $v_o$  remains grounded in the ideal opamp. Consecuently the output resistance is ideally 0.

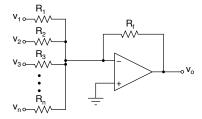

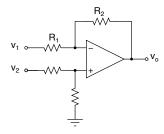

# 2. Summing amplifier

A KCL at the inverting input yields

$$\frac{v_1}{R_1} + \frac{v_2}{R_2} + \dots + \frac{v_n}{R_n} = -\frac{v_o}{R_f}$$

Thus

$$v_{o} = -\left(\frac{R_{f}}{R_{1}}v_{1} + \frac{R_{f}}{R_{2}}v_{2} + \dots + \frac{R_{f}}{R_{n}}v_{n}\right)$$

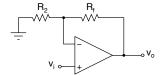

# 3. Non-inverting amplifier

Since the two opamp terminals must be at the same voltage,

$$i_1 = \frac{-v_i}{R_1}$$

and

$$i_2 = \frac{-v_i - v_o}{R_2}$$

But no current flows into the inverting terminal, so  $i_1 = i_2$ . Substituting into this equation and solving for  $v_o$  yields

$$v_o = \left(1 + \frac{R_2}{R_1}\right) v_i$$

Input impedance  $R_i$  is infinite. Output impedance is very low.

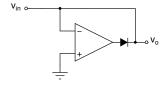

## 4. Voltage follower or buffer amplifier

Since  $R_f = 0$  and this configuration is the same than the non-inverting amplifier, the gain is unity. The input impedance is, however, infinity. So this configuration elliminates loading, allowing a source with a relatively large Thevenin's resistance to be connected to a load with a relatively small resistance.

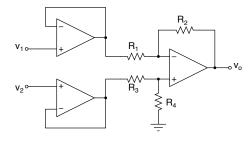

#### 5. Difference amplifier

This circuit provides an output voltage that is proportional to the difference of the two inputs. Applying KCL at the inverting terminal yields

$$i_1 = \frac{v_1 - v_-}{R_1} = i_2 = \frac{v_- - v_o}{R_2}$$

Solving for  $v_o$  and reordering terms gives

$$v_o = \frac{R_1 + R_2}{R_1} v_{-} - \frac{R_2}{R_1} v_1$$

Since  $v_- = v_+ = \frac{R_4}{R_3 + R_4} v_2$ ,

$$v_o = \frac{R_1 + R_2}{R_1} \frac{R_4}{R_3 + R_4} v_2 - \frac{R_2}{R_1} v_1$$

By choosing  $R_1 = R_3$  and  $R_2 = R_4$  one gets that

$$v_o = \frac{R_2}{R_1} (v_2 - v_1)$$

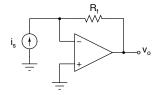

# 6. Current-to-voltage converter

Since the source current  $i_s$  can not flow into the amplifier's inverting input, it must flow thorugh  $R_f$ . Since the inverting input is virtual ground,

$$v_o = -i_s R_f$$

Also, the virtual ground assumption implies that

$$R_i = 0$$

39

for this circuit.

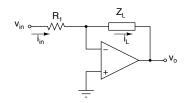

## 7. Voltage-to-current converter

In this cricuit, the load is not grounded but takes the place of the feedback resistor. Since the inverting input is virtual ground,

$$i_L = i_{in} = \frac{v_{in}}{R_1}$$

# 8. Instrumentation amplifier

This amplifier is just two buffers followed by a differential amplifier. So it is a differential amplifier but the two sources see an infinite resistance load.

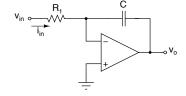

#### 9. Integrator

Let  $v_{in}$  be an arbitrary function of time. The current through the capacitor is  $i_{in} = \frac{v_{in}}{R_1}$ . From the capacitor law,

$$i_C = C \frac{dv_C}{dt}$$

or

$$v_o = -v_C = -\frac{1}{C} \int i_C dt = -\frac{1}{R_1 C} \int v_{in} dt$$

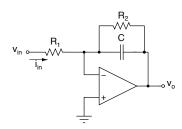

## 10. Active low-pass filter

Here we assume that the input is sinusoidal. Thus we can use the concepts of impedance and reactance and work in the frequency domain. Thus, the circuit is an inverting amplifier, but the feedback resistor as been replaced with  $Z_f$ , the parallel combination of  $R_2$  and C. Therefore,

$$Z_f = \frac{\frac{1}{sC}R_2}{\frac{1}{sC} + R_2} = \frac{R_2}{1 + sCR_2}$$

From the expression for the inverting amplifier's gain,

$$v_o(s) = -\frac{Z_f}{R_1} = -\frac{R_2}{R_1} \frac{1}{1 + sCR_2} v_i(s)$$

which is small for s large.

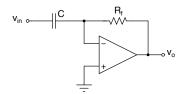

#### 11. Differentiator

Here the input current is determined by the capacitor law,

$$i_{in} = C \frac{dv_{in}}{dt}$$

Thus

$$v_o = -R_f i_{in} = -R_f C \frac{dv_{in}}{dt}$$

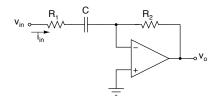

# 12. Active high-pass filter

Like in the low-pass filter, we consider  $v_{in}$  to be sinusoidal and apply impedance concepts. The configuration is again like the inverting amplifier, but the resistor  $R_1$  as been replaced with  $Z_1$ , which is  $R_1$  in series with C. Thus

$$Z_1 = R_1 + \frac{1}{sC} = \frac{sR_1C + 1}{sC}$$

and

$$v_o = -\frac{R_f}{Z_1} = -\frac{sCR_f}{sR_1C + 1}$$

41

which is small for s small.

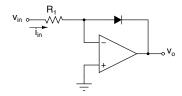

#### 13. Precision half-wave rectifier

In this circuit, the diode conducts when the opamp output is positive and larger than 0.7V, i.e. when the non-inverting inputs exceeds the inverting by  $\frac{0.7}{A_{open-loop}}$  volts, where  $A_{open-loop}$  represents the opamp open-loop gain, taken to be infinity for an ideal device. Thus as soon as the input becomes negative, the diode conducts and the output becomes virtual ground. If the input is positive, the diode is an open circuit and the output is directly connected to the input.

The circuit is used to rectify signals whose amplitude is smaller than the 0.7V required to forward-bias the diode.

### 14. logarithmic amplifier

Here output and diode's voltage are equal in magnitude and of opposite signs. Since

$$i_D \approx I_S exp\left(\frac{v_D}{V_T}\right)$$

where  $V_T$  is the thermal voltage, equal to 25mV at room temperature. It follows that

$$v_o = -v_D = -V_T (log(v_{in}/R_1) - logI_s)$$

and is thus proportional to the logarithm off the input.

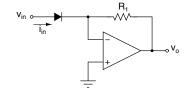

### 15. Antilogarithmic amplifier

The current  $i_{IN}$  is given by

$$i_D \approx I_S exp\left(\frac{v_D}{V_T}\right)$$

or

$$i_{IN} \approx I_S exp\left(\frac{v_{IN}}{V_T}\right)$$

Thus the output voltage is

$$v_O = -i_{IN}R_f \approx I_S R_f exp\left(\frac{v_{IN}}{V_T}\right)$$

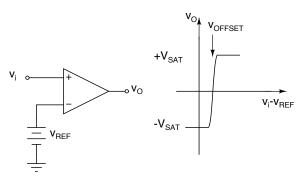

#### 16. Comparator

An opamp can be used as a comparator in a circuit like the one shown below. This is a non-linear circuit in which the output saturates to about 90 % of the positive and negative supply voltages. The polarity of the output voltage depends on the sign of the differential input,  $v_i - v_{REF}$ .

The sketch shows non-ideal characteristics tipically found in opamps. The offset voltage,  $v_{OFFSET}$ , is on the order of few millivolts and causes the transition from low to high to be slightly displaced from the origin.  $v_{OFFSET}$  can be negative or positive, and is zero in an ideal opamp. The posibility of having voltages between plus and minus  $v_{SAT}$ , a consecuense of the finite gain of practical opamps, is also shown. This part of the curve would be vertical if the opamp is ideal. Special integrated circuits (like the MC1530) are specially build to be used as comparators and minimize these non-ideal effects.

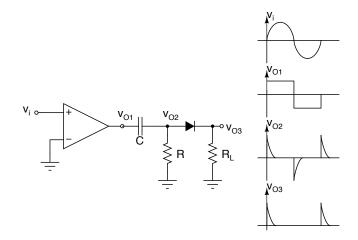

#### 17. Zero-crossing detector

If the inverting input of a comparator is connected to ground, the device's output switches from positive to negative saturation when the input goes from positive to negative, and viceversa. Output  $v_{O1}$  on the following sketch displays this vehavior.

# 18. Timing-marker generator

If an RC network is connected to the output of a zero-crossing detector, capacitor charging and discharging produce the waveform  $v_{O2}$  shown in the above sketch. This signal is rectified to produce the waveform labeled  $v_{O3}$ . The circuit is called a *timing-markers generator*, or TMG, for obvious reasons.

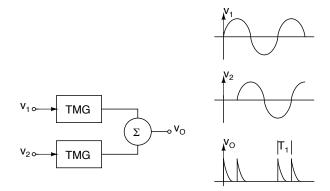

#### 19. Phase meter

Combining two TMG and an adder, as shown in the following figure, one can build the so called *phase meter*. The time difference  $T_1$  is proportional to the phase difference between the two sinusoidal inputs.

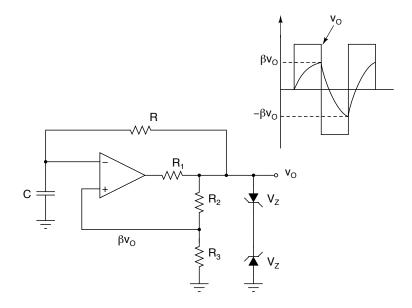

# 20. Square Wave Generator

This circuit is an oscillator that generates a square wave. It is also known as an astable multivibrator. The opamp works as a comparator. Let's assume that the opamp output goes high on power-on, thus making  $v_O = +V_Z$ . The capacitor charges with a time constant  $\tau = RC$ . When the capacitor voltage reaches  $\beta v_O = \frac{R_3}{R_2 + R_3}$ , the opamp output switches low, and  $v_O = -V_Z$  as shown in the graph.

# 4.3 Limitations and Second Order Effects on Real Opamps

# 4.3.1 Gain, Input and Output Resistance

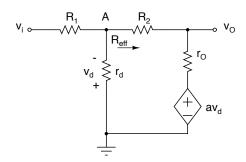

Real operational amplifiers have finite input resistance and gain, as well as non-zero output resistance. We can represent the opamp by its two-port equivalent network, shown below. Analysis of circuits consist on replacing the opamp by its two-port equivalent and performing network analysis.

# **Inverting Amplifier**

# Voltage Gain

After replacing the opamp by its equivalent circuit, the schematic diagram of the inverting amplifier looks as follows.

We can write the two node equations and solve them simultaneously to obtain the voltage gain. However, the algebra becomes simpler if we invoke the voltage divider rule to express the voltage  $v_d$  in terms of the output voltage. This yields

$$v_O = av_d + (-v_d - av_d)\frac{r_O}{R_2 + r_O}$$

After rearranging, this gives

$$v_d = \frac{v_O}{a - (1+a)\frac{r_O}{r_O + R_2}}$$

Since a is always very large, we can approximate 1 + a as a. This gives

$$v_d = v_O/\alpha \tag{4.1}$$

where

$$\alpha = \frac{aR_2}{r_O + R_2}$$

We can now apply KCL to the node between  $R_1$  and  $R_2$  to get

$$\frac{v_i + v_O/\alpha}{R_1} = -\frac{v_O/\alpha}{r_d} - \frac{v_O/\alpha + v_O}{R_2}$$

Multiplying the whole expression by  $\alpha R_2$  gives

$$\alpha \frac{R_2}{R_1} v_i + \frac{R_2}{R_1} v_O = -\left(\frac{R_2}{r_d} + \alpha + 1\right) v_O$$

After rearrangement,

$$A_{v} = \frac{v_{O}}{v_{i}} = -\frac{R_{2}}{R_{1}} \frac{\alpha}{1 + \alpha + \frac{R_{2}}{r_{d}||R_{1}}}$$

A well designed inverting amplifier will use  $R_2 >> r_O$  to avoid excesive loading at the output, and  $R_1 << r_d$  to avoid excesive loading at the input. Under these conditions,

$$A_v = \frac{v_O}{v_i} = -\frac{R_2}{R_1} \frac{a}{1 + a + \frac{R_2}{R_1}}$$

# Input Resistance

By inspection of the circuit diagram,

$$R_{in} = R_1 + r_d || R_{eff}$$

where  $R_{eff}$  is the effective resisitance seen when looking from point A towards the right, as shown in the diagram. Applying a test source  $v_A$  at point A and observing that  $v_A = -v_d$ ,

$$i_A = \frac{v_A + av_A}{R_2 + r_O}$$

so

$$R_{eff} = \frac{v_A}{i_A} = \frac{r_O + R_2}{1 + a}$$

The input resistance then becomes

$$R_{in} = R_1 + r_d || \frac{r_O + R_2}{1 + a}$$

Assuming a well design amplifier,

$$R_{in} = R_1 + \frac{R_2}{1+a}$$

## Output Resistance

Grounding the input and applying a test source  $v_{TEST}$  to the output terminal yields a test current given by

$$i_{TEST} = \frac{v_{TEST}}{R_{eq}} + \frac{v_{TEST} - av_d}{r_O}$$

where

$$R_{eq} = R_2 + R_1 || r_d$$

Applying the voltage divider rule

$$v_d = -\frac{R_1||r_d}{R_{eq}}v_{TEST}$$

which yields

$$R_{OUT} = \frac{v_{TEST}}{i_{TEST}} = R_{eq} \left| \left| \frac{r_O}{1 + a \frac{R_1 || r_d}{R_{cq}}} \right| \right|$$

For a well designed amplifier

$$R_{OUT} = \frac{r_O}{1 + a \frac{R_1}{R_1 + R_2}}$$

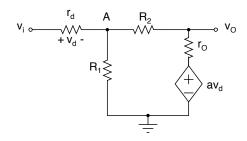

#### Non-inverting Amplifier

After replacing the opamp by its equivalent circuit, the schematic diagram of the non-inverting amplifier looks as follows.

Applying the voltage divider rule to express the output voltage in terms of the voltage at point A,  $v_A$ , yields

$$v_O = \frac{v_A - av_d}{R_2 + r_O} r_O + av_d$$

To elliminate  $v_A$ , express it as  $v_i - v_d$  tp obtain

$$v_O = \frac{v_i - v_d - av_d}{R_2 + r_O} r_O + av_d$$

which, after combining the two terms on the right hand side, cancelling common terms with opposite signs and rearranging, gives

$$v_O = \frac{r_O}{R_2 + r_O} v_i + \frac{aR_2 - r_O}{R_2 + r_O} v_d$$

Solving for  $v_D$  yields

$$v_d = b_1 v_O - b_2 v_i = \frac{R_2 + r_O}{aR_2 - r_O} v_O - \frac{r_O}{aR_2 - r_O} v_i$$

where  $b_1$  and  $b_2$  are defined in the equation. To simplify this expression further, let's invoke the "good design rule" previously established: to avoid output loading, select  $R_2 >> r_O$ . Assuming that the rule is followed,

$$v_d \approx \frac{1}{a}v_O - \frac{1}{a}\frac{r_O}{R_2}v_i$$

Since for amplifiers usually  $v_i < v_O$ , the second term can be neglected and

$$v_d \approx v_O/a$$

Applying KCL at node A and replacing  $v_d$  for  $\frac{v_O}{a}$  yield

$$\frac{v_O/a}{r_d} = \frac{v_i - v_O/a}{R_1} + \frac{v_i - v_O/a - v_O}{R_2}$$

Multiplying the whole expression by  $aR_2$  gives

$$\frac{R_2}{r_d}v_O = \frac{R_2}{R_1}av_i - \frac{R_2}{R_1}v_O + av_i - v_O - av_O$$

which, after rearrangement, becomes

$$A_v = \frac{v_O}{v_i} = \left(1 + \frac{R_2}{R_1}\right) \frac{a}{1 + a + \frac{R_2}{r_d ||R_1|}}$$

Input Resistance

Applying a test source at the input and applying KCL at node A gives

$$i_{TEST} = \frac{v_d}{r_d} = \frac{v_i - v_d}{R_1} + \frac{v_i - v_d - av_d}{R_2}$$

where  $r_O$  as been neglected. Solving for  $v_d$  gives

$$v_d = \frac{r_d ||R_1|| \frac{R_2}{a+1}}{R_1 ||R_2|} v_i$$

Thus,

$$i_i = \frac{r_d ||R_1|| \frac{R_2}{a+1}}{r_d(R_1 || R_2)} v_i$$

and

$$R_{in} = \frac{v_i}{i_i} = r_d \frac{R_1 || R_2}{r_d || R_1 || \frac{R_2}{a+1}}$$

Since for any practical design  $R_2 \ll aR_1$ , and assuming that for a good design  $R_1$  is selected much smaller that  $r_d$ ,

$$R_{in} \approx ar_d \frac{R_1}{R_1 + R_2} = ar_d \frac{1}{1 + \frac{R_2}{R_1}} = r_d \frac{a}{A_{\nu,ideal}}$$

where  $A_{v,ideal}$  is the expected voltage gain for the non-inverting amplifier. Thus, it can be safely assumed that the input resistance will be a few orders of magnitude larger than  $r_d$ , an already large resistance.

**Output Resistance**

Inspection of the circuit diagrams for the inverting and non-inverting amplifiers after the input node is grounded reveals that there is no difference between the two. Thus, our results for the inverting amplifier's output resistance apply to the non-inverting amplifier without modification.

# 4.3.2 Input Bias and Offset Current

Non-ideal amplifier biasing requires a small amount of current to flow into the input terminals. Due to unavoidable imperfections in the manufacturing process, the currents that flow into the inputs,  $I_n$  and  $I_p$ , are not exactly equal. This gives place to two parameters, called *bias* and *offset* currents, normally specified in the opamp data sheets. The bias current is defined as the average current flowing into the inputs.

$$I_B = I_p + I_n$$

The offset currents is absolute value of the difference between the two input currents.

$$I_{OS} = |I_p - I_n|$$

The sense of  $I_B$  is determined by the type of transistor used in the device's input stage, entering and exiting for NPN and PNP input transistors, respectively. The offset current sign can not be predicted and changes from device to device. The offset current is typically an order of magnitude smaller that the bias current.

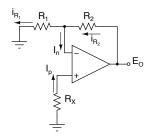

To get an idea of the importance the bias current can have in the operation of a circuit, consider the following diagram.

By considering the bias currents with grounded inputs, we can find out the output error due to the currents. Proper selection of resistor  $R_x$  will allow us to partially cancel out such error, as we will see. We assume that, in spite of the presence of the bias currents, the two input terminals are virtually connected. Thus, from Ohm's law,

$$v_n = v_p = -I_p R_x$$

and

$$i_{R_1} = -\frac{R_x}{R_1} I_p$$

The output error is then given by

$$E_O = -I_p R_x + (I_n - \frac{R_x}{R_1} I_p) R_2$$

If, for example, we neglect the offset current and assume that  $I_p = I_n = 80nA$ ,  $R_x = 0$ ,  $R_1 = 22k\Omega$  and  $R_2 = 2.2M\Omega$ , the output error is  $2.2 \times 10^6 \times 80 \times 10^{-9} = .176V$ , a quantity unaceptable for many applications. We can see, however, that by reducing the size of  $R_2$  the error can be reduced. Also, if we select

$$R_r = R_1 || R_2$$

we can completely cancel out the error due to  $I_B$ , and be left out with smaller error due to  $I_{OS}$ . For further reductions we can select an amplifier with smaller values of  $I_B$  and  $I_{OS}$ , or trim the error down manually.

# 4.3.3 Input Offset Voltage

If the two inputs of an opamp are connected together, ideally the output voltage should be zero. An actual opamp, due to unavoidable fabrication errors, will yield a non-zero output even if the inputs are tied together. To make the output zero, a suitable correcting voltage must be applied at the input. This voltage is called the *input offset voltage* and is represented by  $V_{OS}$ .

The polarity of  $V_{OS}$  is not known in advance. A value of 1mV is typical, with something like 5mV being the maximum. This voltage is amplified with the same gain than the input signal, and can thus lead to a large output error. If the amplifier's gain is, for instance, 1000, the output error can be up to  $\pm 5V$ !

# 4.3.4 Offset Nulling

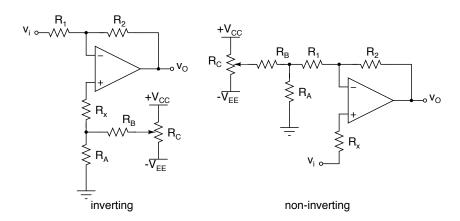

The reduction of errors due to both  $V_{OS}$  and  $I_{OS}$  can be achieved by applying an external dc input voltage such that the output voltage is made zero when no input is present. The required voltage can be obtained from the supplies using a voltage divider network. The correction must be adjusted once the circuit is assembled by means of adjusting a potentiometer.

Setups that can be used for offset nulling are shown below for both inverting and noninverting amplifiers. Resistor values must be selected to make possible to correct for the largest possible offset. It is a good practice to select  $R_B < R_C$  to avoid loading the potentiometer's voltage divider. For the inverting amplifier,  $R_A$  should be much smaller that  $R_x$  to avoid altering the resistance levels. Likewise,  $R_A << R_1$  to avoid altering the gain of the non-inverting amplifier. If this is not feasible,  $R_1$  should be decreased to incorporate  $R_A$  and still have the same gain.

Offset Nulling Networks

# 4.4 Practice Problems

From chapter 2: problems 22 and 30. Also see old exams.