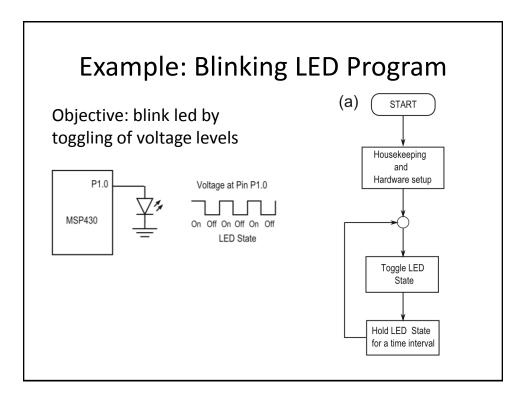

#### MSP430 Assembly Programming

#### Programming Levels

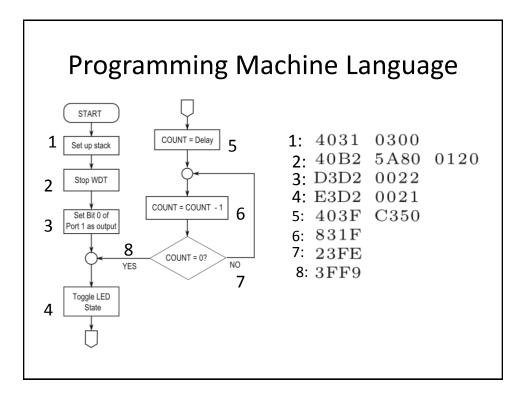

- Machine language

- Description of instructions in terms of 0's and 1's. This is the model for the actual contents in program memory

- Normally presented in Hex Notation.

- Assembly language

- Machine language in human-readable form. Allows better control of program

- High level language

- Preferred by most programmers because of its English like syntaxis and notation.

#### Programming Assembly Language

| mov.w<br>mov.w<br>bis.b<br>xor.b<br>mov.w<br>dec.w | #0x300,SP<br>#0x5A80,&0x012<br>#001,&0x0022<br>#001,&0x0021<br>#0xC350,R15<br>R15 | $\begin{array}{c} \longleftrightarrow D3D2 \\ \Longleftrightarrow E3D2 \\ \Leftrightarrow 403F \\ \Leftrightarrow 831F \end{array}$ | $\begin{array}{c} 5\mathrm{A80}\\ 0022\\ 0021 \end{array}$ | 0120 |

|----------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|

|                                                    | R15<br>0x3FC                                                                      | $\leftrightarrow$ 831F<br>$\leftrightarrow$ 23FE                                                                                    |                                                            |      |

| jnz<br>jmp                                         | 0x3F2                                                                             | $\leftrightarrow$ 3FF9                                                                                                              |                                                            |      |

|                                                    |                                                                                   |                                                                                                                                     |                                                            |      |

There is a one-to-one correspondence between machine language and assembly language instructions

### MSP430 Machine language structure (1/3)

- Length of One, two or three words:

- Instruction word

- Instruction word Source Info Destination Info

- Instruction word (Source or Dest) Info

- 2 operand instructions with source and destination

- 1 operand instructions with dest or source

- O operand instruction: Only one: RETI <u>return from</u> <u>interrupt</u>

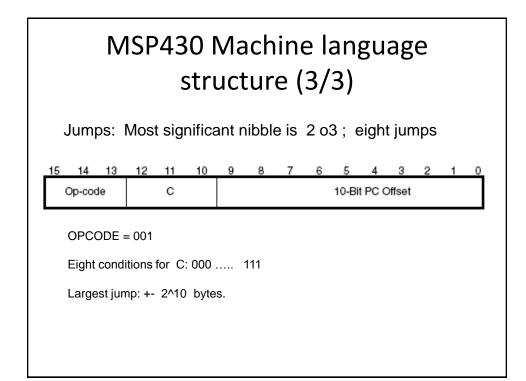

- JUmps

|    | MSP430 Machine language<br>structure (2/3)                |             |        |              |               |             |         |        |         |       |                   |         |            |          |      |

|----|-----------------------------------------------------------|-------------|--------|--------------|---------------|-------------|---------|--------|---------|-------|-------------------|---------|------------|----------|------|

| Tw | Two operand instructions (most significant nibble 4 to F) |             |        |              |               |             |         |        |         |       |                   |         |            |          |      |

| 15 | 14                                                        | 13          | 12     | 11           | 10            | 9           | 8       | 7      | 6       | 5     | 4                 | 3       | 2          | 1        | 0    |

|    | Op-                                                       | code        |        |              | S-F           | Reg         |         | Ad     | B/W     |       | As                |         | D-         | Reg      |      |

|    |                                                           |             |        |              |               |             |         |        |         |       |                   |         |            |          |      |

| 15 | •                                                         | opera<br>13 | and in | nstruc<br>11 | tion (n<br>10 | nost s<br>9 | sign. N | libble | e 1; ro | eti = | = 1300            | ))<br>3 | 2          | 1        | 0    |

|    | •                                                         | •           | 12     |              | 10            |             | •       |        |         | 5     | = 1300<br>4<br>Ad | 3       | 2<br>D/S-F | 1<br>leg | <br> |

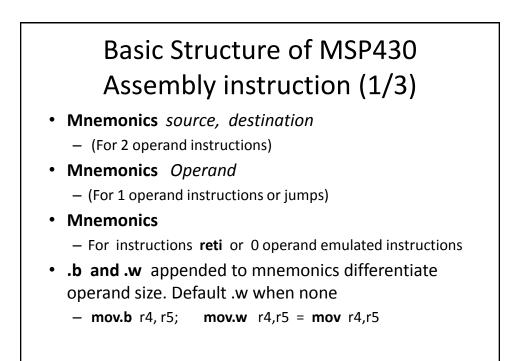

### Basic Structure of MSP430 Assembly instruction: general cases (3/3)

- Operands are written with a syntax associated to the addressing mode

- Operands can be

- Register names

- Integers

- Integers can be:

- Base ten integers (no suffix or prefix)

- Base 2 (suffix b or B)

- Base 16 (suffix h or H, or prefix 0x; it cannot begin with a letter)

- Base 8 (suffix q or Q)

#### MSP430 Addressing modes

| N         | Mode                           | Syntax | DATA location                                                                   | Source | Destination |

|-----------|--------------------------------|--------|---------------------------------------------------------------------------------|--------|-------------|

| LOCATIONS | Immediate                      | #X     | Data is X                                                                       | OK     | X           |

| Ö         | Register                       | Rn     | ls in Rn                                                                        | OK     | ОК          |

| Ц         |                                |        |                                                                                 |        |             |

|           | Direct                         | Х      | at address X                                                                    | OK     | ОК          |

| LOCATIONS | Absolute                       | &X     | at address X                                                                    | OK     | ОК          |

|           | Indexed                        | X(Rn)  | At address Rn + X                                                               | OK     | ОК          |

|           | Indirect                       | @Rn    | At address Rn                                                                   | OK     | X           |

| ГОС       | Indirect with<br>autoincrement | @Rn+   | At address Rn. In<br>addition Rn<br>incremented by data<br>size after execution | ОК     | x           |

ivotes: Kn is a register name; X is an integer number (valid constant)

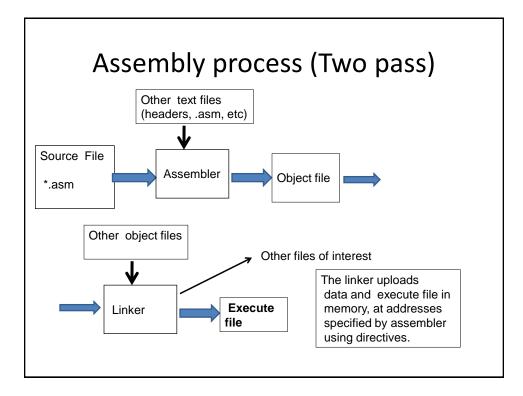

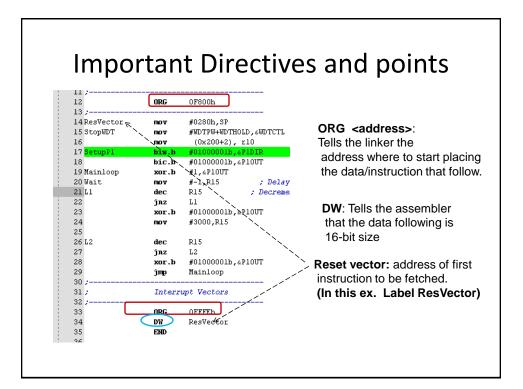

# Assembly process (1/2): Source and assembly

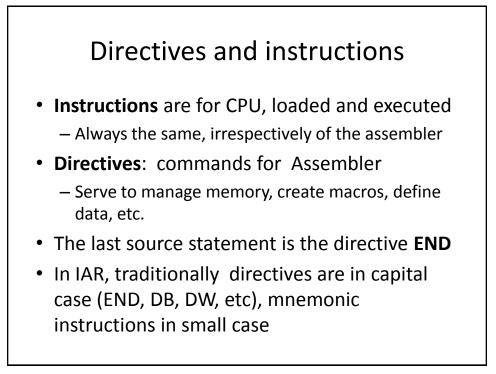

- To **assembly** is to convert assembly language to machine language.

- To dissasembly goes from machine to assembly

- Source file: text file containing assembly instructions and directives

- Directive: 'instruction' for assembler and linker, not loaded into program memory

- Source statement: each line in the source file

- **Object file**: file with machine language instructions that results from **assembler**

- Execute file: machine language file loaded into memory. It results from linker

#### Assembly process (2/2) : Assembler

- Interpreter: assemblies one line at a time

Line interpreter: only one line

- Assembler: Usually reads the source fi

- Two-pass assemblers: allows use of defined constants, labels, macros, comments, etc.

- Read the source once to decode user defined vocabulary

- Format of source statetment in two-pass assembler:

- [Label] [mnemonics] [operands] [;comment]

#### **Important Facts**

- Source statement: A line in the source file

- Source fields (may consist of only one)

Label Mnemonics Operand(s) ;Comment

- Label always goes on first column

- Comment always follows a semicolon (;)

- On the first column, <u>always a label, blank, or a</u> <u>comment, nothing else</u>

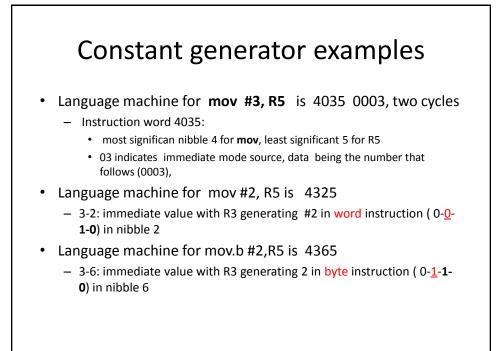

#### Constant generators registers R3 and R2 in MSP430

- For certain immediate mode source values, behavior is similar to register mode by using a constant generator register.

- Values #0, #1, #2, #-1 are generated by R3.

- Value #4 is automatically generated by R2

- Absolute value 0 in O(Rn) is generated by R2

- Change is transparent to user; must be taken into account for timing and instruction size (see ex. 4.4)

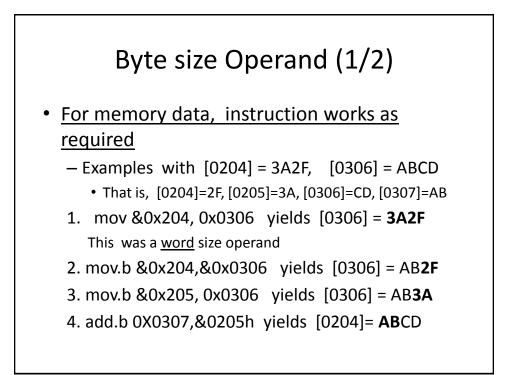

#### **INSTRUCTIONS**

#### MSP430 Instruction Set

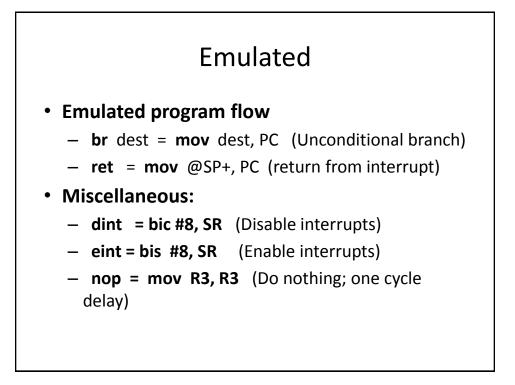

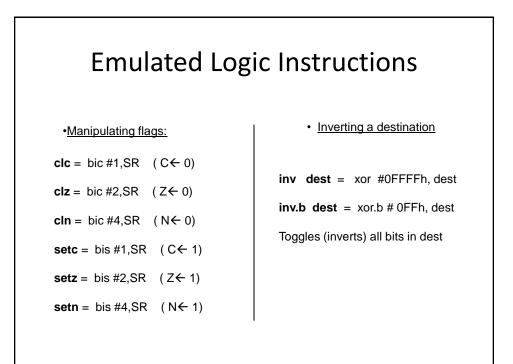

- 27 Core Instructions and 24 emulated instructions

- Core instructions are the machine native language instructions, supported by hardware.

- Emulated instructions are "macros" translated automatically by the assembler to an equivalent core instruction

- Defined to make programming easier to read and write

- Already standard.

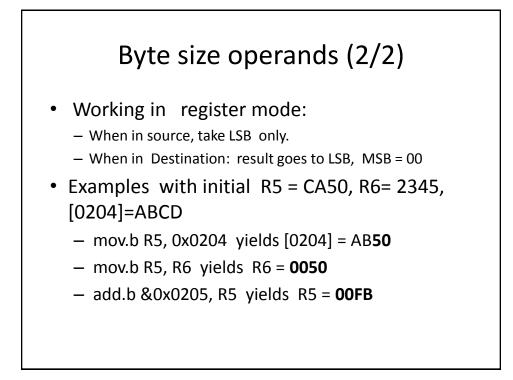

mov src, dest (dest ← src)

mov src, dest = mov.w src, dest; mov.b src, dest

- push src (1. SP $\leftarrow$  SP-2; 2. (SP)  $\leftarrow$  src)

- **push.b** only pushes the byte, but moves SP two places.

- pop dest = mov @SP+, dest

- This is an emulated instruction

- pop.b dest moves only byte, but SP ← SP+2 anyway

- Verify the your understanding by checking the following instructions in your assembler.

- push #0xABCD, push.b #0xCD, pop r10, pop.b r11

- swpb src Swaps low and most significant bytes of word src

No byte operation allowed

#### Some Remarks on push and pop (2/3)

- Correct push R6 push R5

- `` other instructions

- pop R5

- pop R6

- 'Pop' the last item you 'pushed'

- Incorrect (be careful) push R6 push R5 `` other instructions pop R6

- pop R5But you can define

- macro swp R5,R6 this way! Ha ha

#### Remarks on stack management

- Push and Pop operations are managed with the stack pointer SP

- Once a data is popped out, it cannot be retrieved with a stack operation

Use mov for this purpose

- You can work with items in stack the same way you work with memory.

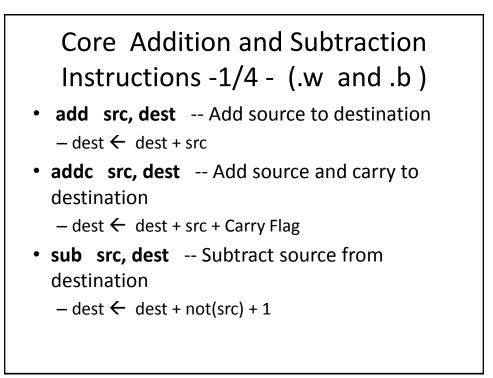

#### **Arithmetic Instructions**

\*\*\* Affect flags \*\*\*

# Normal Flag effects for addition and subtraction

- C = 0 if not carry; C= 1 if carry

- For addition: C=1 means a carry is generated

- For subtraction: C=0 means a borrow is needed;

- Z=0 if destination is not zero, Z=1 if result is zero (cleared)

- N = most significant bit of destination

- V = 1 if overflow in addition or subtraction, V=0 if not overflow

- <u>Addition overflow</u> if two signed integers of same sign yields a result of different sign

- <u>Subtraction overflow</u> if difference between numbers of different sign has the sign of subtrahend

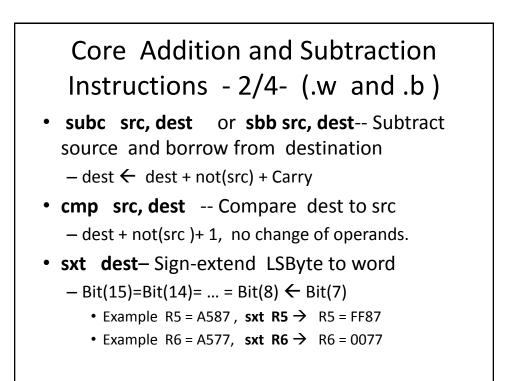

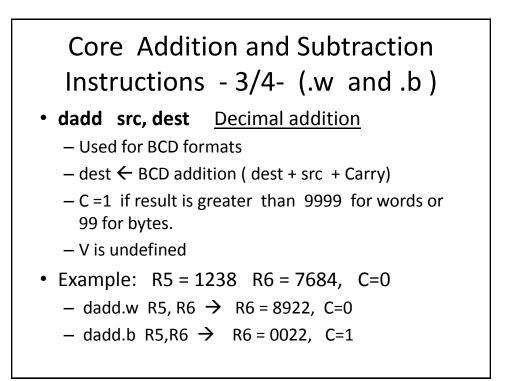

#### Core Addition and Subtraction (3/4): Using Compare (cmp)

- **comp** src, dest is usually encoded to compare two numbers A=dest, B=src, in order to take a decision based on their relationship.

- Decision is made with a conditional jump.

- Conditions directly tested in MSP430 are

- (1) If A=B then....; (2) If A  $\neq$  B then ....

- (3) If  $A \ge B$  then .... [for signed and unsigned]

- (5) If A<B then ..... [for signed and unsigned]

- (7) If A <0 then ....

#### Emulated arithmetic operations

- **adc dest** = addc #0,dest (add carry to dest)

- dadc dest = dadd #0, dest (decimal addition of carry)

- **dec dest** = sub #1,dest (decrement destination)

- decd dest = sub #2,dest (decrement dest twice)

- **inc dest** = add #1,dest (increment destination)

- incd dest = add # 2, dest (increment dest twice)

- **sbc dest** = subc #0, dest (subtract borrow)

- tst dest = cmp #0, dest (Ojo C=1, V=0 always)

#### Logic Bitwise Instructions

And MSP430 logic bitwise instructions

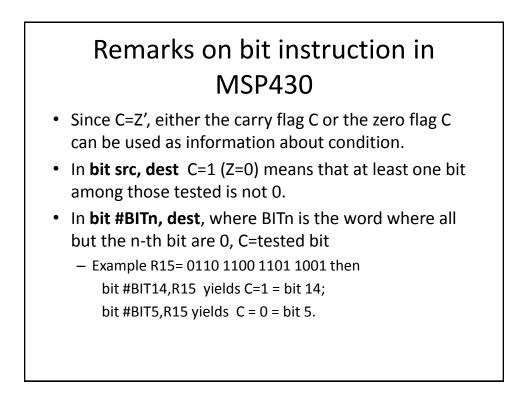

#### Effects on Flags

- Flags are affected by logic operations as follows, under otherwise indicated:

- Z=1 if destination is cleared

- Z=0 if at least one bit in destination is set

- C= Z' (Flag C is always equal to the inverted value of Z in these operations)

- N = most significant bit of destination

- V = 0

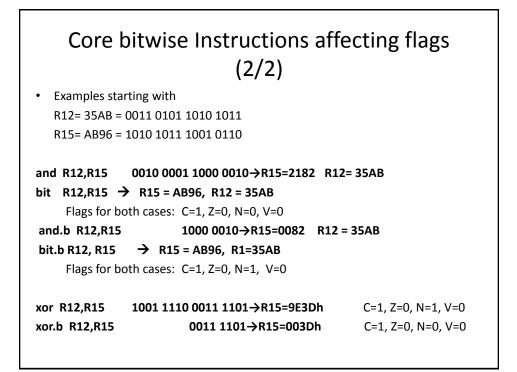

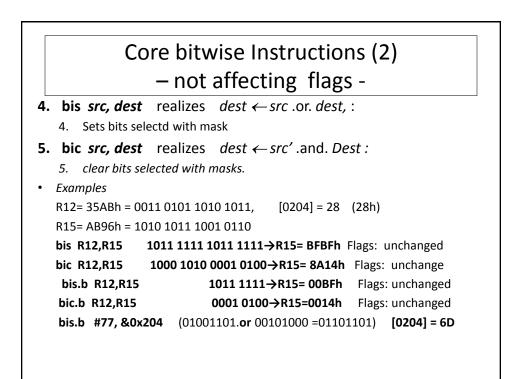

## Core bitwise Instructions affecting flags (1/2)

1. and src, dest realizes dest ← src .and. Dest

- 2. xor src, dest realizes dest ← src .xor. Dest

- a) Most common, but not exclusive, use is for inverting (toggle) selected bits, as indicated by the mask (source)

- b) Problem: show that the sequence xor r5,r6 xor r6,r5 xor r5,r6 has the effect of swapping the contents of registers r5 and r6.

- 3. bit src, dest realizes src .and. dest but only affects flags

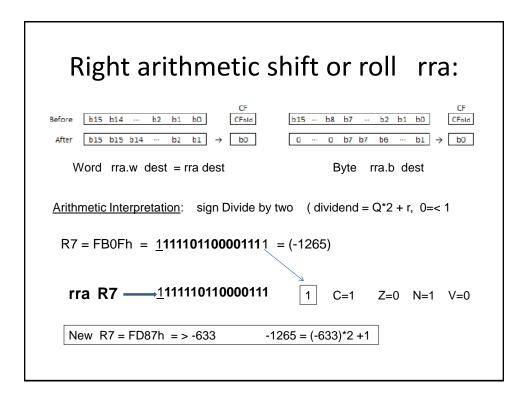

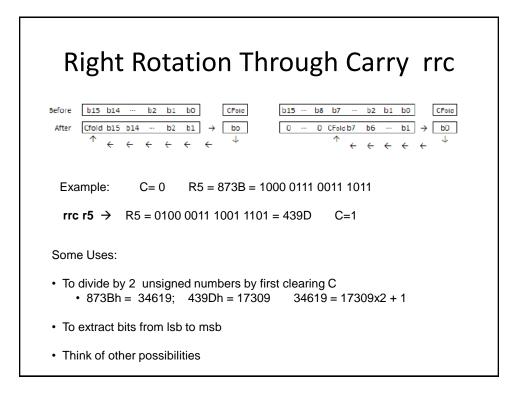

#### Rolls and Rotates in MSP430

#### Rolling (Shifting) and Rotating Data bits

- Two core instructions:

- Right rolling arithmetic: rra dest

- Right rotation through Carry: rrc dest

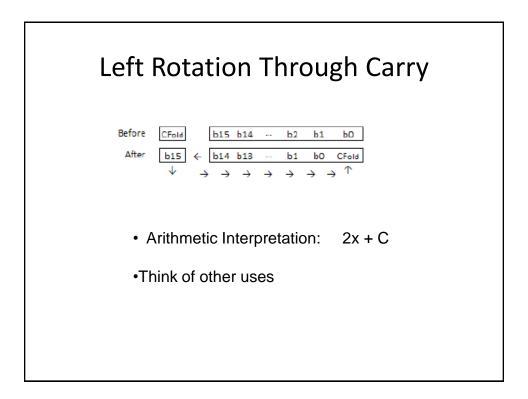

- Two emulated instructions

- Left rolling arithmetic: rla dest = add dest, dest

- Rotate left through carry: rlc dest = addc dest, dest

| Left rollings                                                                                                          |       |         |  |    |    |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|-------|---------|--|----|----|----|--|--|--|

| Left rolling:<br>rla dest = add dest,dest ➔ multiply by 2 (may need carry)<br>Other uses: extract bits from msb to lsb |       |         |  |    |    |    |  |  |  |

| . (                                                                                                                    | CF    |         |  |    |    |    |  |  |  |

| Before                                                                                                                 | CFold | b15 b14 |  | b2 | b1 | bO |  |  |  |

| After                                                                                                                  | b15 ← | b14 b13 |  | b1 | bO | 0  |  |  |  |

|                                                                                                                        |       |         |  |    |    |    |  |  |  |

|                                                                                                                        |       |         |  |    |    |    |  |  |  |

|                                                                                                                        |       |         |  |    |    |    |  |  |  |

|                                                                                                                        |       |         |  |    |    |    |  |  |  |

#### **Program Flow Instructions**

Do not affect flags

#### Jumps 1/2 (Core)

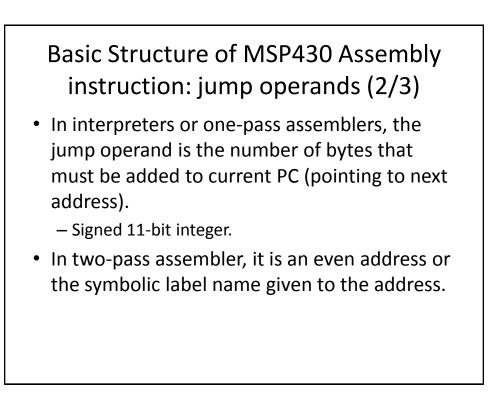

- jz/jeq label or address (jump if zero/equal)

- jnz/jneq label or address (jump if not zero/equal)

- jc/jhe label or address (jump if carry/ higher or equal -- for unsigned numbers)

- jnc/jlo label or address (jump if not carry/ lower-- for unsigned numbers)

#### Jumps and subroutine 2/2 (Core)

- jge label or address (jump if greater or equal for signed numbers)

- jl label or address (jump if less -- for signed numbers)

- jn label or address (jump if flag N=1)

- jmp label or address (unconditional jump)

- call dest

- calls subroutine;

- dest follows addressing mode conventions

- reti : return from interrupt